Part Number: DAC38RF89

在调试时,204B接口通道速率跑10G的时候一切正常,跑12G的时候,SYNC信号出现偶尔会拉低,引起重同步。除了和SERDES PLL相关的两个寄存器0X3B,0X3C做了对应修改,其他寄存器都没有变化。所以也试过其他的通道速率,8G也是正常的,11G会出现不稳定,所以让我觉得是因为速率高,引起不稳定的问题。DAC是直采,没有用的上变频和PLL。8G和10G能正常跑,基本配置应该没有问题,不知是否配置需要注意什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

非常感谢您的回复!我这边的配置,在各个速率下都能工作,但在Lrata速率大于10G时就出现问题,所以问题应该是出现在和serdes相关的寄存器。在Lrata速率为12G的时候Serdes PLL相关的配置为x"3b1801"; x"3c8051" ,DACLK为2.4G,得到时钟为 2400/2/4*10=3G,Serdes PLL输出时钟为3G。另一种是x"3b0801",x"3c8029"得到时钟为 2400/2/2*5=3G。两种情况都能跑通,但SYNC还是偶尔会掉。使用的模式是LMFSHd =41121,双DAC单LINK模式。芯片应该是能够满足要求的,但我一直在排查可能出现的问题,这款芯片配置比较少,配置流程也不复杂。不知道您们是否见过类似的问题,来帮助我对问题的解决,谢谢!

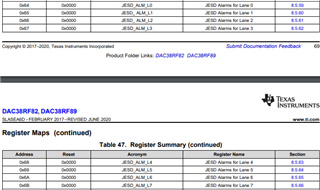

请您在出错时读出警报来缩小错误的排查范围。目前我们认为这可能是信号完整性问题。

当出错时,请您参考以下ppt:

1832.General Alarms for All Converters.pptx

LMFSHd=41380,但数据组帧时发现,组合起来的数据是24bit,不符合204B接口的四字节处理,

这是标准 的JESD204 F =3 模式。所有的FPGA IPs,例如Xilinx、Intel JESD204 都支持该种模式。如不支持,请您参考TI的JESD204 IP。