Part Number: AFE7769

我司在使用AFE7769的过程中发现以下几个问题:

1:MU的单band的初始化过程中,如果在初始化过程中,将中心频点移动,QMC校准就无法生效,此时0X94--0X9B寄存器始终为0,想请教一下这个是什么原因造成的;

如果初始化过程中没有移频,0X94-0X9B的寄存器就正常;

2:当AFE7769在使用2个FDD的频段时,JESD204建链存在问题,因为在使用过程中只用了AFE7769的LANE0,1,2,3的4个通道,双band的初始化JESD204B的建链过程,

如果用getJesdRxLinkStatus检测到状态是1010那么就可以正常建链,如果是0010那么就无法建链,此时需要将TX复位一下也可以成功建链,但是这个此时的建链偶尔会

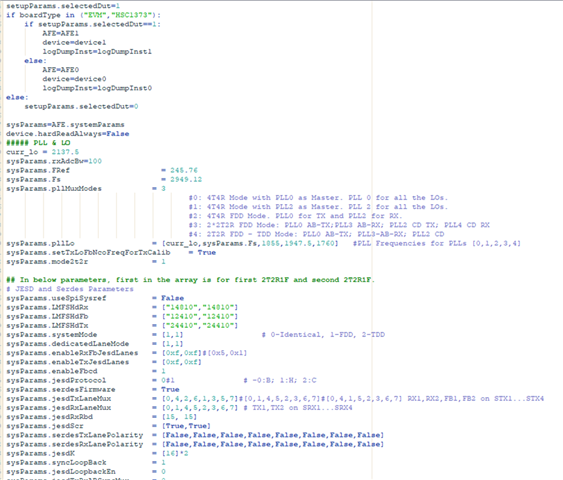

出现复位一次无法建链需要复位2次甚至3次的现象。下图是双BAND的配置需求:

| DUAL_BAND | 2T2R2FB | 带宽 | 射频通道 | 中心频点(MHz) | LANE通道 | LMFS | SYNC信号对应引脚 | LANE RATE | |

| MU | RX | 200MHZ | RX1 | 2137.5 | STX0,1 | 24410 | V5 | 9.83Gbps | RX2 POWER OFF |

| 200MHZ | RX3 | 1855 | STX2,3 | 24410 | C5 | 9.83Gbps | RX4 POWER OFF | ||

| TX | 200MHZ | TX1 | 1947.5 | SRX0,1 | 24410 | Y5 | 9.83Gbps | TX1使用FB1校准 | |

| 200MHZ | TX3 | 1760 | SRX2,3 | 24410 | A5 | 9.83Gbps | TX3使用FB2校准 | ||

| FB | MU可以不用FB,因为没有DPD的需求 |