Part Number: DAC38RF86

Hi,

Currently using DAC38RF86EVM for signal generator design. However, the following problems are encountered:

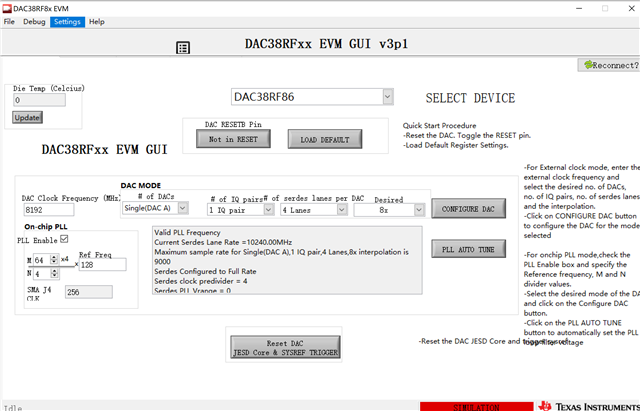

1. the DAC38RF8X EVM GUI V3P1 version of the GUI used, but there is a problem with the GUI display, as shown in Figure, not all of it can be displayed, please ask how to solve this problem;

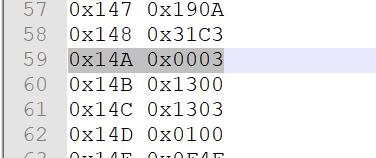

2. when using the DAC38RF8X EVM GUI V3P1 version of the GUI configuration, it is found that the value of the corresponding register in the configuration file exported from the GUI is not the same as the set value, the problem may be a problem with that version and may require corresponding optimization;

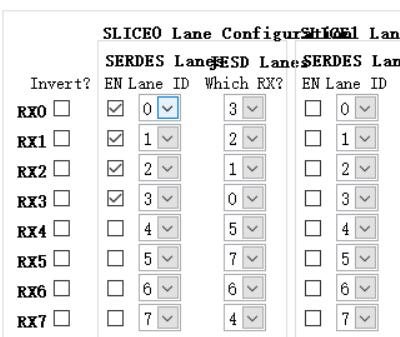

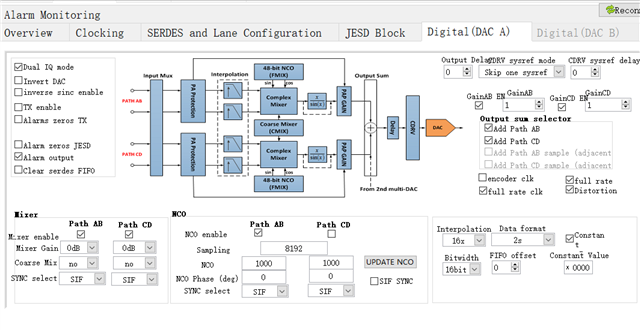

3. when using DAC38RF86, DAC38RF86EVM board clock chip reference clock is 122.88MHz, using DAC on-chip PLL, the reference clock is 128MHz, DAC is 8192MHz, single (DAC A), 4 Lane, interp 8x configuration,as shown in Figure above, serdes clk for DAC clock 1/4 (DIV = 16, MPY = 0x02 (4x)), found that the channel synchronization on, but no output signal, please, what is the problem?

4. In addition, need DAC38RF8X EVM GUI V2.0 version, I wonder if someone can provide.

Thanks!