Other Parts Discussed in Thread: AWRL6844, SYSCONFIG, AWR1843

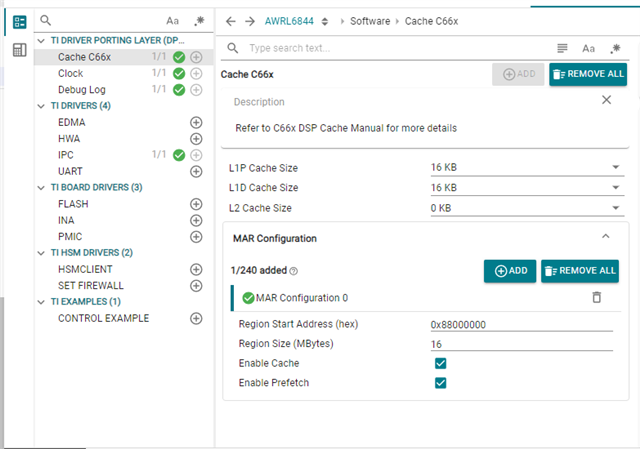

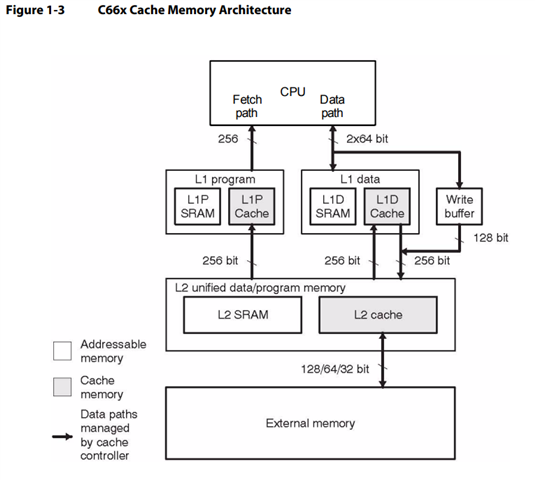

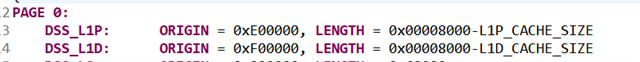

hello, we found that the D1P memory in AWRL6844 DSP core dose not used in incabin radar demo code. As the picture showed behind.

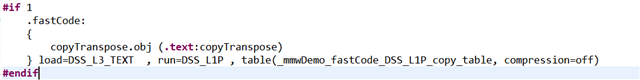

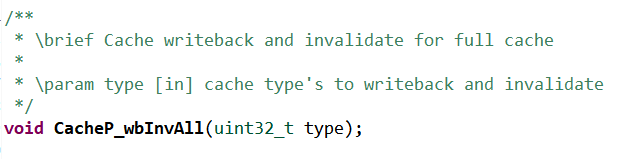

During our software developement, we have tried to use the D1P. For example, we have configured the 16KB D1P to cache , and we put some test code in it. however, the code in the D1P can not run normally as we want it to. Then, DSP core project go exit.

We just want to know that how to use the D1P correctly in DSP?