Part Number: AWR2243BOOST

你好,目前我正在尝试对多块AWR2243BOOST进行级联,通过MCU连接多块AWR2243BOOST的J5或J6引脚中的SPI_CS(J6的引脚6)、SPI_CLK(J5的引脚13)、SPI_MOSI(J6的引脚12)、SPI_MISO(J6的引脚14)、HOSTINT(J6的引脚16)、MCU将Master板(其中一块设为Master,其余的设为Slave)的SYNC_OUT(J5的引脚18)接入MCU的时钟驱动的输入,其余Slave板的SYNC_IN(J5的引脚9)接入时钟驱动的输出;对于每块板,还接了PGOOD(J5的引脚14)用于查看AWR的电源状态。目前的问题如下:

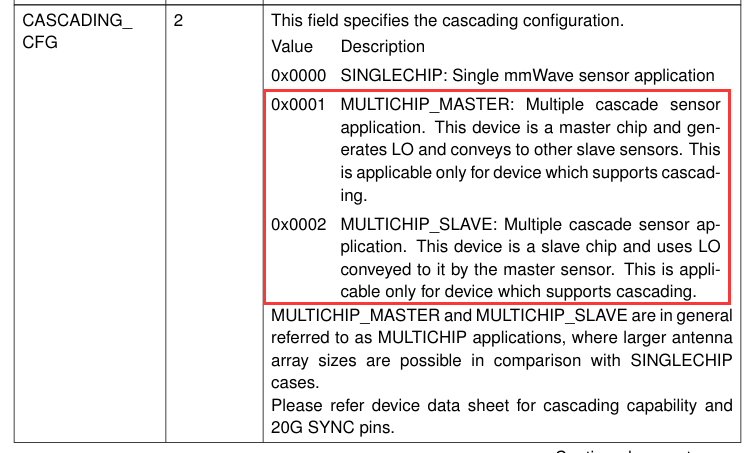

1、查看mmWaveRadar Interface Control Document 文档中的AWR_RF_STATIC_CONF_SET_MSG 发现,如图所示: ,对于级联而言,如果两块板一块设为Master(对应0x0001),一块设为Slave1(对应0x0002),如果有多块Slave的话,全都是0x0002吗?还是会一次递增?(比如Slave2对应0x0003),如果全都是0x0002的话,那么Master是如何区分不同的Slave的呢?

,对于级联而言,如果两块板一块设为Master(对应0x0001),一块设为Slave1(对应0x0002),如果有多块Slave的话,全都是0x0002吗?还是会一次递增?(比如Slave2对应0x0003),如果全都是0x0002的话,那么Master是如何区分不同的Slave的呢?

2、通过设置好Master与Slave后,按照 Cascaded device mode 给出的表依次对Master与Slave下发指令,但是发现并没有数据,于是通过抓取SYNC_OUT的信号发现并没有信号,请问可能的原因是什么?