Hi

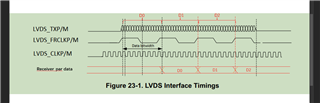

我们正在调试AWR2944 想用LVDS 发送数据 FPGA 接受处理。 但是我看手册上只给出了一个简单的时序图(如下图),其中frame clk 在valid sample data 器件才有效,在接收端我想用这个frame clk 作为串转并后面的并行数据的clk, 但是这样是不是存在第一个解出来的是无效数据(D0前面的数据),并且最后一个有效数据推不出来的问题?是不是我们哪里没理解对? frame clk 是否可以当作时钟来用

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.