尊敬的TI团队,

您好!以下是我的问题描述:

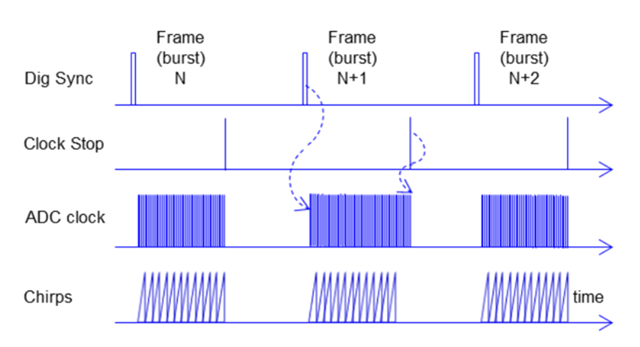

在此文档“”www.ti.com/.../swra574“中,我找到关于DIG_SYNC信号如何硬件触发主或从芯片的时序图,即Figure 5.,我对这幅图有几点疑问:

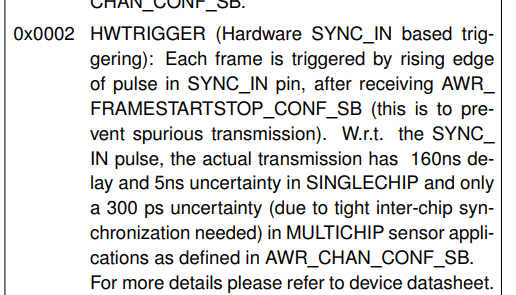

1.若不设置触发延时,Frame的启动时间是否为DIG_SYNC信号的下降沿结束的那一刻?如果情况是Frame无法在DIG_SYNC下降沿结束就立刻启动,而是会有一定时延,这个时延取决于什么,时延大概为什么时间量级?

2.如第一条问题所述,如果Frame的触发不存在时延或时延几乎可以忽略,那从芯片的外部20GHZ LO输入是否是必须的?因为似乎从芯片用内部20GHZ LO作为斜坡信号频率源,主芯片只使用DIG_SYNCOUT控制从芯片的发射,也不会影响Chirp的发射同步,例如实现Beam Forming或者TDM-MIMO。所以如果不使用主芯片分配20GHZ LO作为从芯片的外部20GHZ LO输入,MIMO模式或Beam Forming模式下分别会产生什么问题?

提前感谢TI工程师宝贵的建议,期待你们的回复,另附图: