Other Parts Discussed in Thread: AWR2544, DCA1000EVM

使用的oob例程,LVDS输出adc数据,将通过自制的FPGA去接收LVDS数据。

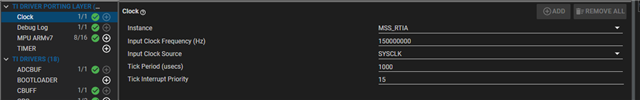

core clock

HW_WR_REG32(CSL_MSS_TOPRCM_U_BASE + CSL_MSS_TOPRCM_HSI_CLK_SRC_SEL, 0x333);

问题1、写寄存器这个是配置PLL_PER_CLK (1000MHz) ?其中0x333 /0x222有什么区别呢?如何理解?

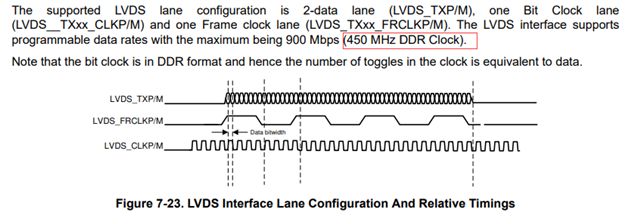

AWR2544 datasheet DDR clock 是450Mhz

/* Enable all lanes available on the platform*/

initCfg.lvdsCfg.lvdsLaneEnable = 0x3U;

initCfg.lvdsCfg.ddrClockMode = 1U;//DDR时钟模式设置为1

initCfg.lvdsCfg.ddrClockModeMux = 1U;DDR模式时钟复用设置为1

使用DCA1000(使用bat脚本调用DCA1000EVM_CLI_Control.exe)也能采集到数据

示波器能抓到CSI2 / LVDS Differential Frame Clock的信号 20Hz/50ms 与雷达frame配置一致

抓不到CSI2 / LVDS Differential Clock 、CSI2 / LVDS Transmitter, Differential Data Output, Lane 0 、CSI2 / LVDS Transmitter, Differential Data Output, Lane 1 的信号 示波器支持350Mhz以内 可能时钟速度大 抓不到

问题2、也就是说OBB例程中使用LVDS接口输出adc数据 lvds时钟就是450Mhz?

问题3、PLL_PER_CLK 、DDR_CLK 以及与寄存器配置之间有什么关系,或者存在什么样的计算公式(第一次使用雷达的LVDS 不太懂这个)?

谢谢.