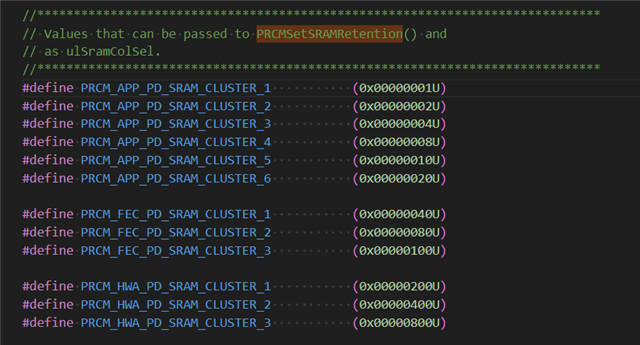

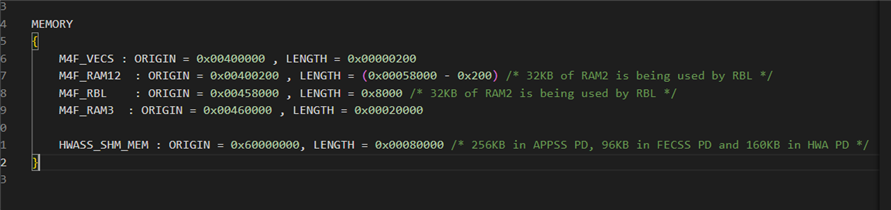

在进入深度睡眠前,会调用PRCMSetSRAMRetention函数来保留SRAM,根据函数PRCMSetSRAMRetentiond的注释SRAM一列的大小为64KB,根据宏定义,我注意到一共只有12列,12*64KB=768KB,SRAM的大小为1MB,似乎并不能对应上,后面剩下的内容是什么地址,不能保留吗?同时,SRAM和地址是怎么对应的,第一列PRCM_APP_PD_SRAM_CLUSTER_1,表示的就是地址0-64k-1吗,第二列表示的是地址64k-128K?。

我注意到此宏定义:1-6列表示的是APP_PD_SRAM这与link.cmd中似乎并不能对应上

void PRCMSetSRAMRetention(unsigned long ulSramColSel, unsigned long ulModeFlags)

{

uint32_t regVal;

int32_t mask;

uint8_t value;

if((ulModeFlags & PRCM_SRAM_LPDS_RET) != 0U)

{

// Control for RAM Memory Clusters 1,2,3 in APP PD

mask = (PRCM_APP_PD_SRAM_CLUSTER_1 | PRCM_APP_PD_SRAM_CLUSTER_2 | PRCM_APP_PD_SRAM_CLUSTER_3);

value = ulSramColSel & (unsigned long)mask;

regVal = HW_RD_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_APP_PD_RAM_STATE);

regVal = ((regVal & ~((unsigned long)mask)) | value);

HW_WR_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_APP_PD_RAM_STATE, regVal);

// Control for RAM Memory Clusters 4,5 in APP PD

mask = (PRCM_APP_PD_SRAM_CLUSTER_4 | PRCM_APP_PD_SRAM_CLUSTER_5);

value = (ulSramColSel & (unsigned long)mask) >> 3;

regVal = HW_RD_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_APP_PD_RAM_GRP1_STATE);

regVal = ((regVal & ~((unsigned long)mask >> 3)) | value);

HW_WR_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_APP_PD_RAM_GRP1_STATE, regVal);

// Control for RAM Memory Cluster 6 in APP PD

mask = (PRCM_APP_PD_SRAM_CLUSTER_6);

value = (ulSramColSel & (unsigned long)mask) >> 5;

regVal = HW_RD_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_APP_PD_RAM_GRP2_STATE);

regVal = ((regVal & ~((unsigned long)mask >> 5)) | value);

HW_WR_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_APP_PD_RAM_GRP2_STATE, regVal);

// Control for RAM Memory Cluster 1 in FEC PD

mask = (PRCM_FEC_PD_SRAM_CLUSTER_1);

value = (ulSramColSel & (unsigned long)mask) >> 6;

regVal = HW_RD_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_FEC_PD_RAM_STATE);

regVal = ((regVal & ~((unsigned long)mask >> 6)) | value);

HW_WR_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_FEC_PD_RAM_STATE, regVal);

// Control for RAM Memory Clusters 2,3 in FEC PD

mask = (PRCM_FEC_PD_SRAM_CLUSTER_2 | PRCM_FEC_PD_SRAM_CLUSTER_3);

value = (ulSramColSel & (unsigned long)mask) >> 7;

regVal = HW_RD_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_FEC_PD_RAM_GRP4_STATE);

regVal = ((regVal & ~((unsigned long)mask >> 7)) | value);

HW_WR_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_FEC_PD_RAM_GRP4_STATE, regVal);

// Control for RAM Memory Clusters 1,2,3 in HWA PD

mask = (PRCM_HWA_PD_SRAM_CLUSTER_1 | PRCM_HWA_PD_SRAM_CLUSTER_2 | PRCM_HWA_PD_SRAM_CLUSTER_3);

value = (ulSramColSel & (unsigned long)mask) >> 9;

regVal = HW_RD_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_HWA_PD_RAM_GRP3_STATE);

regVal = ((regVal & ~((unsigned long)mask >> 9)) | value);

HW_WR_REG32(CSL_TOP_PRCM_U_BASE + CSL_TOP_PRCM_PSCON_HWA_PD_RAM_GRP3_STATE, regVal);

}

}