Other Parts Discussed in Thread: TMUX1133

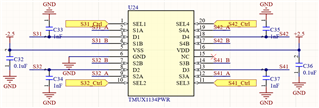

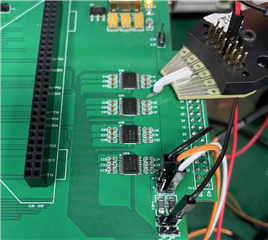

需求是两个模拟信号快速切换,选用了TMUX1134这款模拟开关芯片

PCB完成后,发现电路板的延时非常高,对TMUX1134芯片进行延时测试,与在线技术人员交流后对方表示可能确实存在问题,让我在论坛发帖

想确认两个问题:1.我的测试方法是否正确,标准的测试方法是什么样的? 2.芯片这样的性能表现是否正常

1. 测试环境

电压源*2:提供模拟开关的输入电压

FPGA:提供500K频率的1.8Vpp时钟

示波器:带宽4GHz,采样率20GSa/s

直流探针:直接和芯片引脚接触,测量芯片上输入输出的信号质量

200Ω电位器:用作终端匹配负载

2. 测试结果

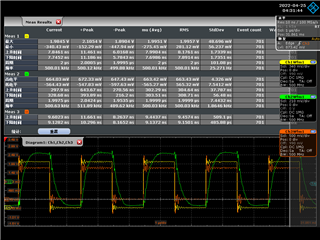

2.1 芯片上时钟信号测试

模拟开关输入端的两个信号,接入电压值分别为 +0.6V和 -0.5V

首先测试接入芯片的时钟信号质量(500K时钟)。

通道1(黄色)为FPGA输出的时钟:测量点为FPGA输出时钟信号的排针

通道2(绿色)为应接光开关位置的终端输出(未接负载):测量点为光开关实际放置位置的排母

通道3(橙色)为芯片接收到的时钟信号:测量点为S42_Ctrl(20引脚)

可以看出芯片接收到的时钟信号虽然是通过杜邦线引入,但是信号质量几乎没有变差:FPGA输出的时钟上升下降沿为~8ns,片接收到的时钟信号上升下降沿为~10ns

芯片上时钟信号测试

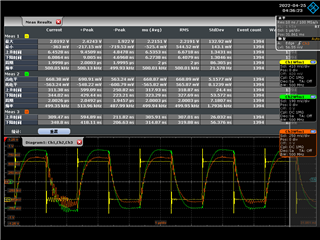

2.2 芯片输出信号测试(未接负载)

在未接负载的情况下,测试芯片输出的电压信号质量。

通道1(黄色)为FPGA输出的时钟:测量点为FPGA输出时钟信号的排针

通道2(绿色)为应接光开关位置的终端输出(未接负载):测量点为光开关实际放置位置的排母

通道3(橙色)为芯片切换完成后直接输出的电压信号:测量点为S42(18引脚)

可以看出芯片切换完成后直接输出的电压信号上升下降沿已经非常的差了,

与光开关实际放置位置的排母上的电压信号几乎是一样的,都是在~300ns

芯片上未接负载时输出信号测试

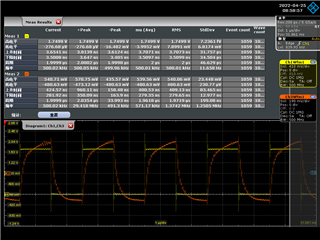

2.3 芯片输出信号测试(接200Ω匹配负载)

在接200Ω匹配负载的情况下,测试芯片输出的电压信号质量。

通道1(黄色)为FPGA输出的时钟:测量点为FPGA输出时钟信号的排针

通道3(橙色)为芯片切换完成后直接输出的电压信号:测量点为S42(18引脚)

在光开关位置的排母上接入了200Ω电阻,故没有测试该点信号。

可以看出在接匹配负载后,芯片切换完成后直接输出的电压信号上升下降沿仍然很差。

芯片上接入200Ω匹配负载时输出信号测试