请教一下,规格书上说如果不使用内部DCDC,VDDR接的就是内部LDO。那怎么判断芯片是使用内部DCDC还是内部LDO呢,是芯片自动感应,还是外面人为设置 ?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

请教一下,规格书上说如果不使用内部DCDC,VDDR接的就是内部LDO。那怎么判断芯片是使用内部DCDC还是内部LDO呢,是芯片自动感应,还是外面人为设置 ?

谢谢!

芯片内部的电源使用分布图不知道能否公布一个,我们想了解下电源使用究竟是什么原理

查看6.3节:https://www.ti.com.cn/cn/lit/ug/swcu117i/swcu117i.pdf

另CC2640r2f使用cjtag,不需要连接TDO TDI

如果Vddr是NC,有没有烧录不上的风险

无论是LDO还是DCDC,VDDR都不能悬空

如不愿提供原理图,则参照参考设计https://www.ti.com.cn/tool/cn/LAUNCHXL-CC2640R2#design-files

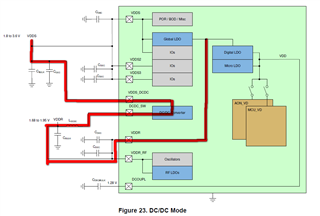

Maximum efficiency is obtained by using the internal DC/DC converter, and it requires an external inductor

(LDCDC) and capacitor (CDCDC). The components should be placed as close as possible to the

CC13xx/CC26xx device and it is important to have a short current return path for from the CDCDC ground

to the pad on the chip (see Section 4.7). In addition, the bulk capacitor on VDDS should be placed close

to the VDDS_DCDC-pin. The actual value of LDCDC, CDCDC and CBULK vary from device to device.

For the actual values, see the device-specific reference design.

When operating in DC/DC mode, the power system dynamically switches between the Global LDO and

DC/DC converter depending on the required load to achieve maximum efficiency. If VDDS drops below

2.0 V, the DC/DC converter will be less efficient than the LDO and the device will run in global LDO mode.

For systems operating with VDDS less than 2.0 V, consider either global LDO or external regulator mode

to save component cost and board area.

硬件设计审查按照这里的步骤操作:

https://www.ti.com.cn/tool/cn/SIMPLELINK-2-4GHZ-DESIGN-REVIEWS