Part Number: CC2640R2F

你好!

我使用cc2640r2f与cc2642做一个调试。有两个问题

1. cc2640r2f做slvae,cc2642为central。

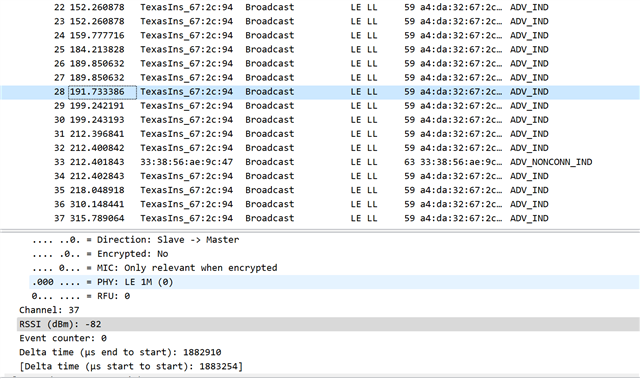

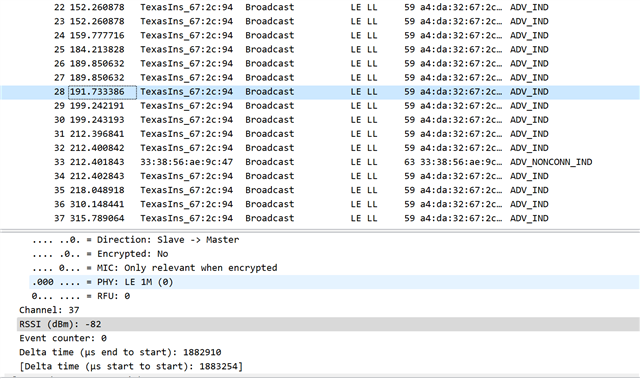

在cc2640r2f广播正常的情况下,cc2642 反复connect都连接不上。这种情况下,需要怎么处理?

2. 在距离拉远,在抓包获取到功率在-85左右,发送的广播报很久才能够抓取到,这个是有什么限制吗?需要怎么解决这个问题。

-85的接收功率,应该还是正常的功率范围。

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: CC2640R2F

你好!

我使用cc2640r2f与cc2642做一个调试。有两个问题

1. cc2640r2f做slvae,cc2642为central。

在cc2640r2f广播正常的情况下,cc2642 反复connect都连接不上。这种情况下,需要怎么处理?

2. 在距离拉远,在抓包获取到功率在-85左右,发送的广播报很久才能够抓取到,这个是有什么限制吗?需要怎么解决这个问题。

-85的接收功率,应该还是正常的功率范围。

谢谢!

你好!

我现在在做一下RC时钟的测试。

使用RCOSC的时候,看了一下有几个配置信息?

1. 下面的配置意思,理解是否准确?

// #define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x1 // External LF clock---这个是直接应用一个时钟吗?

//#define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x2 // LF XOSC ----这个配置是打开外部的时钟源?

#define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x3 // LF RCOSC ---这个是内部RC震荡器?

2. 我想对比测试时钟精度,如果打开外部32.768的时钟,是不是打开#define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x2 这个配置就可以了?

IOCPortConfigureSet(IOIDn, IOC_PORT_AON_CLK32K, IOC_STD_OUTPUT); ---这个配置到外部管脚,是否需要调整?

谢谢!

// #define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x1 // External LF clock 外部时钟源,需要使用DIO接入

#define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x2 // LF XOSC 外部32.768K晶体

// #define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x3 // LF RCOSC 内部LF RC

如果打开外部32.768的时钟,是不是打开#define SET_CCFG_MODE_CONF_SCLK_LF_OPTION 0x2 这个配置就可以了?

是的

IOCPortConfigureSet(IOIDn, IOC_PORT_AON_CLK32K, IOC_STD_OUTPUT); ---这个配置到外部管脚,是否需要调整?

IOIDn中的n需要改为未使用的具体IO引脚号