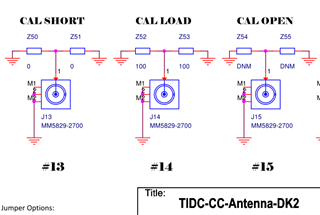

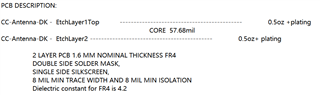

我注意到TIDC-CC-Antenna-DK2的设计文档中有三个校准件,分别是SHORT、LOAD、OPEN,这是做为VNA测试校准用的,那么它的PCB设计走线应该需要严格控制阻抗吧。

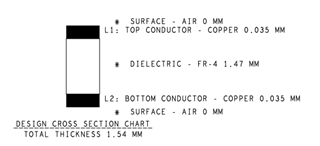

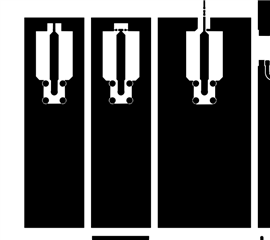

查看走线信息:线宽W=0.69mm,线距G=0.15mm;

再根据叠层信息:2-Layer,H=1.47mm,FR-4(4.2 or 4.6?)

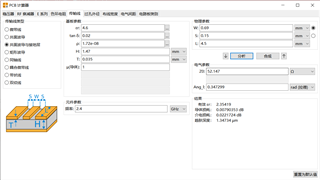

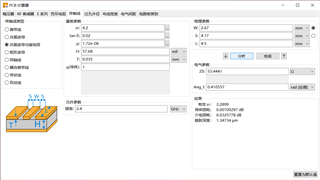

用阻抗计算工具计算如下

当FR-4的介电常数为4.6时结果如下:

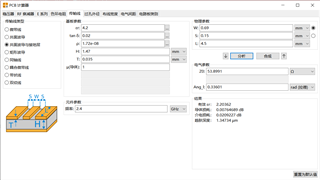

当FR-4的介电常数为4.2时结果如下:

可见差异不大。

但是问题来了,我注意到CC-ANTENNA-DK这个版本的参考设计的叠层信息和走线设计和DK2差异很大:

查看gerber,走线宽度W=2.67mm,间距G=4.17mm。

为什么两个版本的走线不一样呢?有什么特殊原因吗?