Part Number: CC1310

您好:

我目前使用cc1310作为spi slave同另外的rsic-v的芯片通信,现在发现收到的数据偶尔会有错位的现象,有没有什么办法能够调整这个miso的输出相位的?

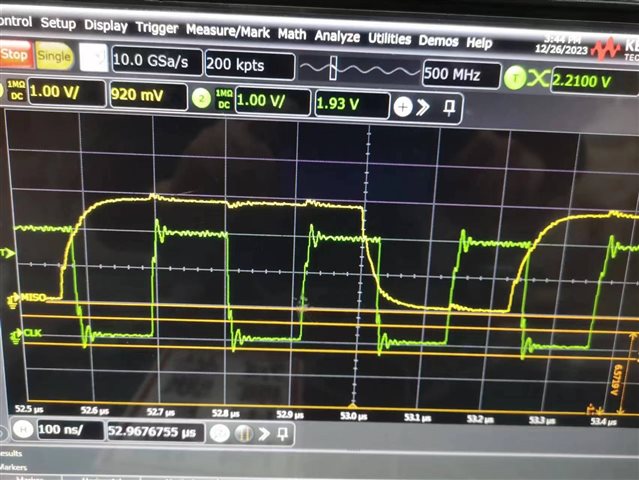

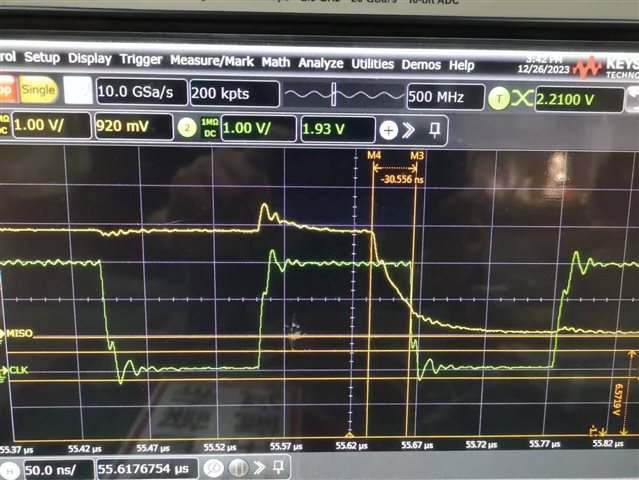

spi master是 rsic-v的ch32v307 ,采用的是spi mode2,spi slave也是mode2;通讯有错位,波形图如下:绿色是clk,黄色为miso;经常会有比如0xF6 变为0xF2的情况;

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

SPI_Params_init(&spiParams);

spiParams.frameFormat = SPI_POL0_PHA1;

spiParams.mode = SPI_SLAVE;

spiParams.transferCallbackFxn = transferCompleteFxn;

spiParams.transferMode = SPI_MODE_CALLBACK;

slaveSpi = SPI_open(Board_SPI_SLAVE, &spiParams);

CC1310这边的spi配置。

您好,查看您的代码

SPI帧格式中,时钟极性为0,可以看出与SPI mode 2是一致

SPI配置目前看起来是没有问题的

您可以尝试以下方面:

1.降低时钟速率,看看是否能减少数据错位

2.检查信号线干扰,确保MISO线和时钟线不受干扰