专家好,

平台:CC2530+Z-STACK2.5.1a,

问题描述:新项目需使用多路ADC,

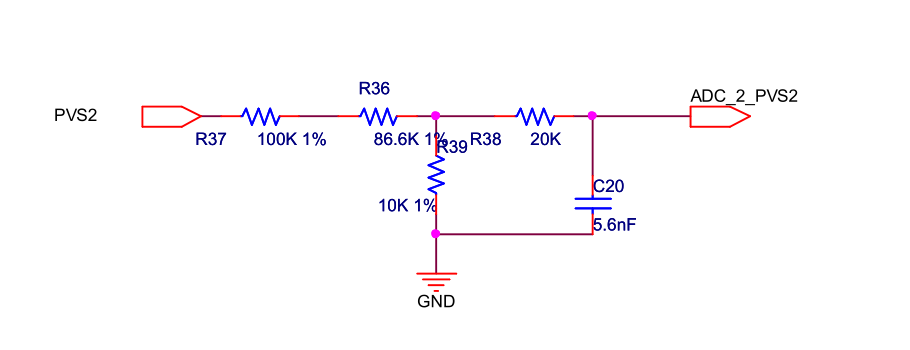

目前发现P0_4采样端电压在非采样期间其电压会被拉低。采样期间电平又恢复正常。采样电路及波形图如下。

问:如何解释?是协议栈里面配置的问题吗?

端口配置如下:

//将P0.0-P0.5配置为模拟IO口

P0DIR&=~0X3F;

P0SEL|=0X3F; //外部设备功能

APCFG = 0x3F; //模拟IO使能

ADC用的协议栈API.

另,想屏蔽串口,是否直接定义 HAL_UART FLASE即可?

项目急,盼回复!