Part Number: TINA-TI

Other Parts Discussed in Thread: OPA855

Dear Engineers,

Hello. I am currently designing a 1 GHz-bandwidth transimpedance amplifier (TIA) and plan to implement it using the OPA855 operational amplifier together with a photodiode whose junction capacitance is 0.65 pF. I have carried out simulations in TINA, but I have encountered several points of confusion during the process.

I would sincerely appreciate it if you could offer me some guidance or suggestions. Thank you very much for your time and support.

My questions are as follows:

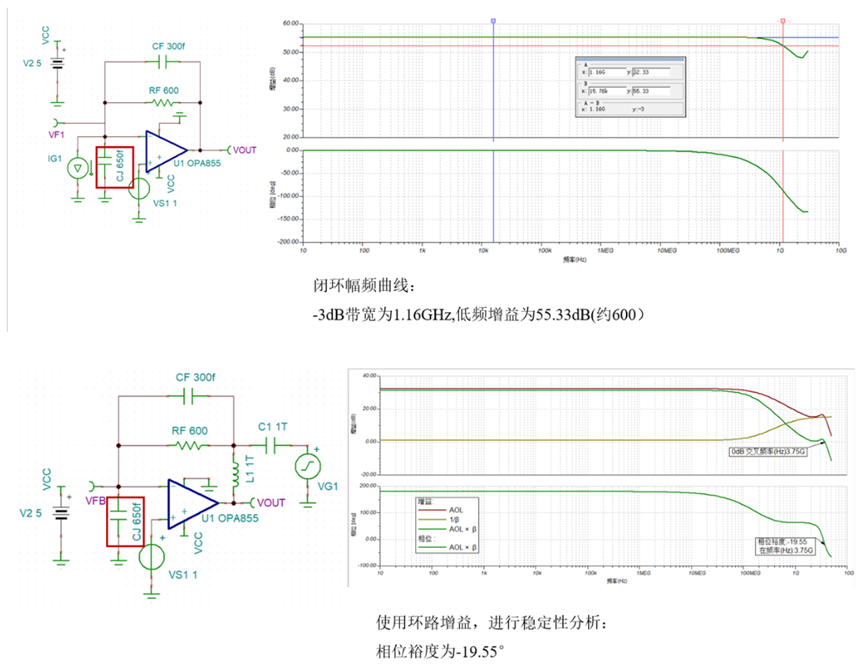

(1) Initially, I assumed that the OPA855 model already included the input capacitance, so I set CJ to represent only the photodiode junction capacitance of 0.65 pF. Under this condition, the AC analysis showed a bandwidth of 1.13 GHz, but the phase margin was only –20°.

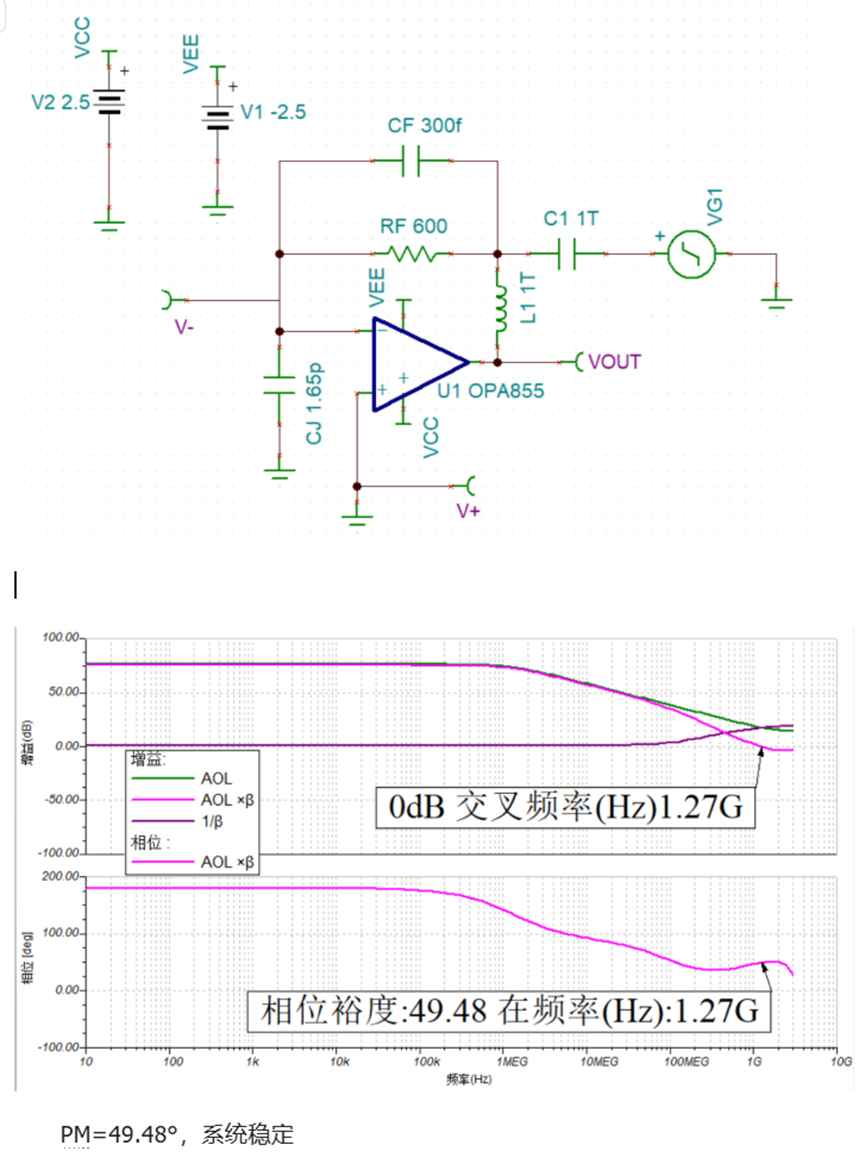

I then increased the capacitance at the junction node to 1.65 pF. With this change, the bandwidth became 1.11 GHz, while the phase margin improved significantly to 50°.

Could you please explain the reason for this behavior?

(2) If the PCB is fabricated according to the schematic I provided, is this design feasible from an engineering perspective? As far as I understand, the parasitic capacitance and inductance of the PCB will significantly affect a transimpedance amplifier. In addition, the capacitance values of 0.3 pF and 1.65 pF are extremely small—especially 0.3 pF. How can such small capacitances be realized in practical hardware?

(3) If my current component selection is not appropriate, I would appreciate any suggestions you could offer.

(4) Is it feasible to achieve a 1 GHz-bandwidth transimpedance amplifier through careful design?

Thanks.

JINGLIN