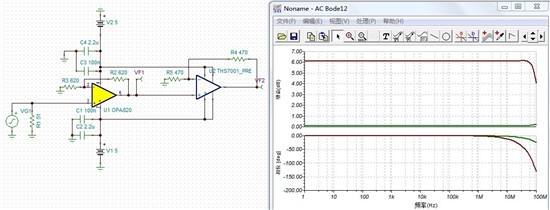

Other Parts Discussed in Thread: OPA820, THS7001

我前级用OPA820做跟随 测试感觉很好

后面直接级联ths7001的前级放大

刚开始设置的反馈电阻为3.9k,增益电阻为1.2k,输出不接电阻直接用示波器探头测试发现芯片自激

在输出接入51欧姆的电阻后测试发现自激现象消失 但是带宽只能到达800khz

所以我打算按datasheet上说的将Rf设置为499欧 由于条件限制 我设置为470欧 在tina仿真时发现效果蛮好

但是实际测试发现芯片一直自激 无论是否在输出串联电阻

电路图如下所思

请各位老师帮忙分析一下 谢谢