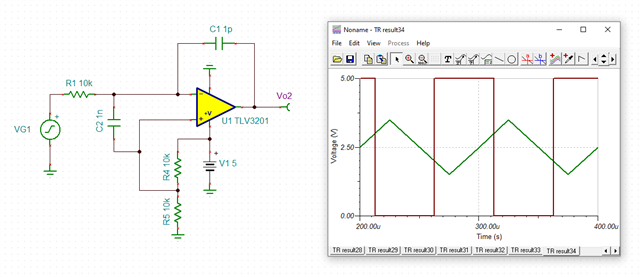

Part Number: TLV3801

各位TI专家好:

打算使用高速比较器TVL3801,看到电阻配置迟滞那一章,有几个问题很疑惑

1.手册里前文提到外部迟滞电路需要正反馈,后文描述的迟滞电路电阻却加在了反向输入端,为什么不矛盾呢?

2.增加了迟滞电路之后LVDS输出会不会偏离了LVDS的标准,对后级采集比较输出脉冲的FPGA的LVDS接收端是否有影响呢?

3.迟滞电压设置是否有范围上限最大能设置多少?

感谢您的回答!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

感谢您的耐心!

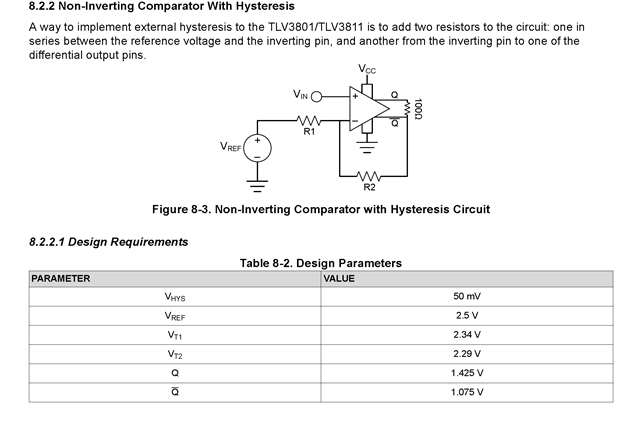

这里主要说的是避免从比较器的输出到负输入的任何寄生电容反馈,因为这会导致不稳定和振荡:

在没有电容反馈的情况下,即使源阻抗有点高(R1=10k),一切都还好:

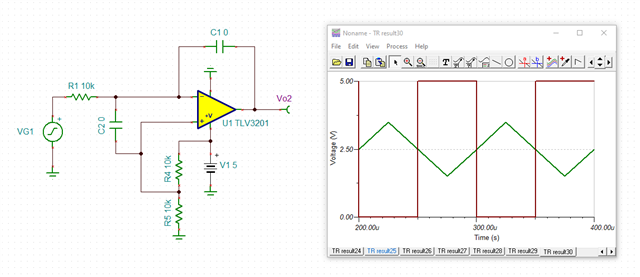

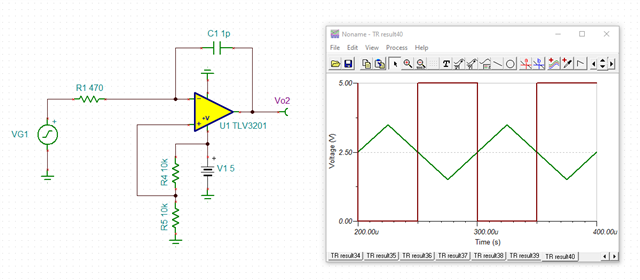

但在寄生电容(C1=1pF)引起的小电容反馈的情况下,会出现不稳定性:

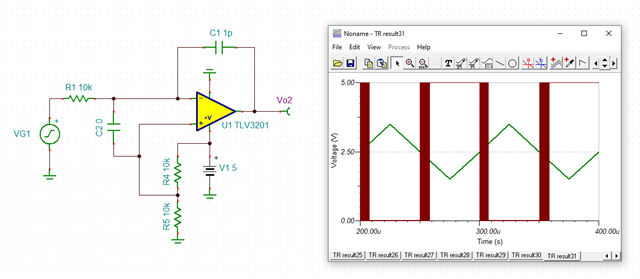

不稳定的原因很简单:当输出翻转时,C1将比较器的反向输入提升到错误的方向,从而破坏翻转。这相当于形成了迟滞电路相反功能的电路。解决办法就是在输入端加一个小电容:

更好的解决方法是使信号源为低阻抗:

或者通过避免或最小化从输出到输入的寄生杂散电容,如第一次仿真所示。

通过电路图和仿真看,它会影响滞回电路的计算结果。