TI的工程师您好:

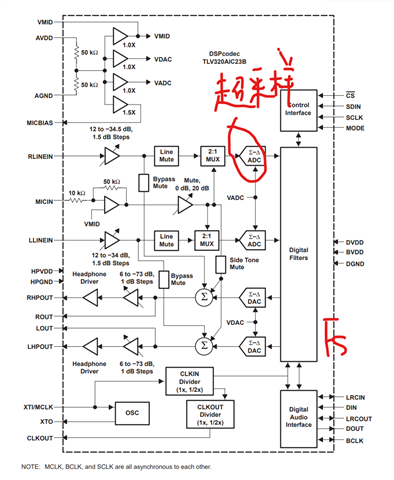

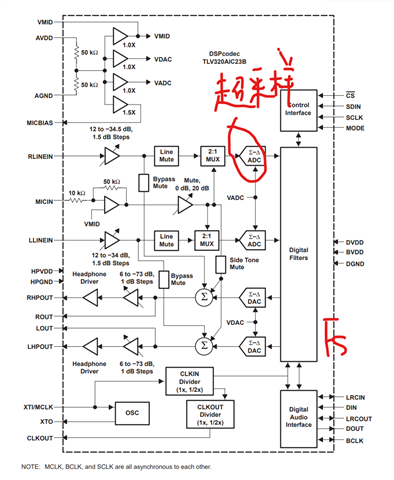

目前我们公司正在使用这一颗codec进行图纸绘制,请帮忙确认我理解的这颗芯片adc 部分的抗混叠滤波实现是否正确。

贵司的这颗TLV320芯片内部自带数字滤波功能,请问linein 进来的模拟信号是否是先经过ADC的超采样?(如果是,请问超采样的采样频率是多少?),然后再经过数字滤波来达到抗混叠滤波的目的。

如果是这样,请问我信号进芯片之前的RC滤波的截止频率是否只需要不超过超采样频率的1/2就可以。

多谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

TI的工程师您好:

目前我们公司正在使用这一颗codec进行图纸绘制,请帮忙确认我理解的这颗芯片adc 部分的抗混叠滤波实现是否正确。

贵司的这颗TLV320芯片内部自带数字滤波功能,请问linein 进来的模拟信号是否是先经过ADC的超采样?(如果是,请问超采样的采样频率是多少?),然后再经过数字滤波来达到抗混叠滤波的目的。

如果是这样,请问我信号进芯片之前的RC滤波的截止频率是否只需要不超过超采样频率的1/2就可以。

多谢

您好,

最高采样率到96KHZ,具体见数据表3.3.2 Audio Sampling Rates章节;

TLV320AIC23B内部集成的是Delta-Sigma ADC,主要包括Delta-Sigma 调制器和数字滤波器,Delta-Sigma 调制器以非常高的速率对输入信号进行采样,并转换成1bit位数据流,之后,数字滤波器使用该采样数据,将其转换成高分辨率低速数字代码。注意,这里的数字滤波器不是抗混叠滤波的目的。

任何超过采样频率一半的输入信号都会产生混叠信号,因此,抗混叠滤波器是加在信号输入端以滤除产生混叠信号的频率。

Amy Luo:

你好,我们的TLV320AIC23B 是否也支持这种特性,下面是从互联网上找到的一些关于Sigma-Delta ADC 抗混叠设计的说明

对于 Sigma-Delta ADC, 它具有非常高的分辨率,而且噪声很低。因为它采用了过采 样的技术,因此对于前端的抗混叠滤波器的要求也大大降低,一般一个简单的 RC 低通滤 波器就足够了。这类 ADC 的线性度也非常好。但是它付出的代价是采样速率的降低。一 般这类 ADC 的采样速率都相对较低。另外,由于内部滤波器对于模拟信号的突变和通道 的切换需要相对长的建立时间,而且输出的数据与模拟输入之间有比较长的延时,所以这 类 ADC 适用于那些模拟信号近似于直流或变化很慢的应用,如温度测量、压力测量等等。