Part Number: TLV320AIC3101

Other Parts Discussed in Thread: TLV320AIC31

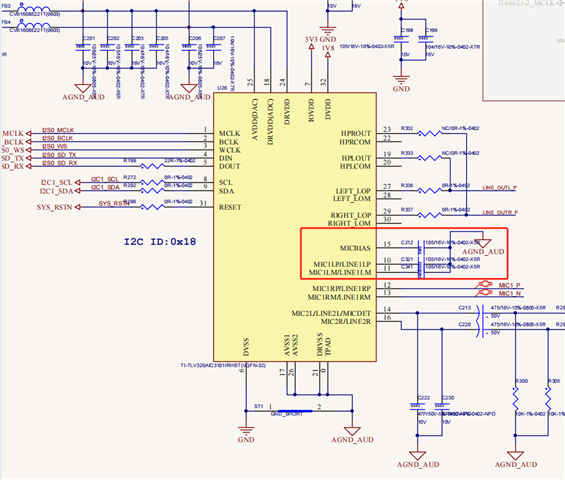

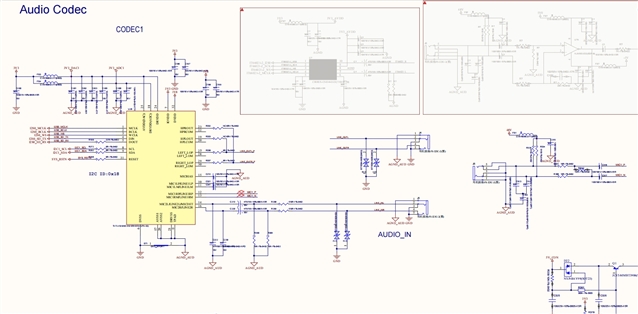

最近在海思SS528平台上调试TLV320AIC3101的驱动,硬件做了一路MIC输入、一路LINE IN 输入和一路LINE OUT,原理图如下:

调试了好久,一直没有声音输出,我的寄存器配置:

void soft_reset(unsigned int chip_num)

{

// soft reset

tlv320aic31_write(IIC_device_addr[chip_num], 1,0x80);

msleep(10);

/*CLKDIV_IN uses MCLK*/

tlv320aic31_write(IIC_device_addr[chip_num], 102, 0x32);

#if 1

/*PLL disable and select Q value*/

tlv320aic31_write(IIC_device_addr[chip_num], 3, 0x10);

#else

// PLL enable

tlv320aic31_write(IIC_device_addr[chip_num], 3, 0x81);/* P=1 Q=16*/

tlv320aic31_write(IIC_device_addr[chip_num], 4, 0x20);/* J=8 */

tlv320aic31_write(IIC_device_addr[chip_num], 5, 0x00);

tlv320aic31_write(IIC_device_addr[chip_num], 6, 0x00);

#endif

// left and right DAC open

tlv320aic31_write(IIC_device_addr[chip_num], 7, 0x0a);/* 48 kHz */

// sample

tlv320aic31_write(IIC_device_addr[chip_num], 2, 0xaa);/* FS = FSref/6 */

// ctrl mode

tlv320aic31_write(IIC_device_addr[chip_num], 8, 0x00);/* slave mode */

// Audio Serial Data Interface Control

tlv320aic31_write(IIC_device_addr[chip_num], 9, 0x07);/* I2S mode,16bit */

// Data offset = 0 bit clocks

tlv320aic31_write(IIC_device_addr[chip_num], 10, 0x00);

// Audio Codec Digital Filter Control Register

tlv320aic31_write(IIC_device_addr[chip_num], 12, 0x50);

tlv320aic31_write(IIC_device_addr[chip_num], 14, 0x00);

// The ADC PGA is not muted.

tlv320aic31_write(IIC_device_addr[chip_num], 15, 0x00);

tlv320aic31_write(IIC_device_addr[chip_num], 16, 0x00);

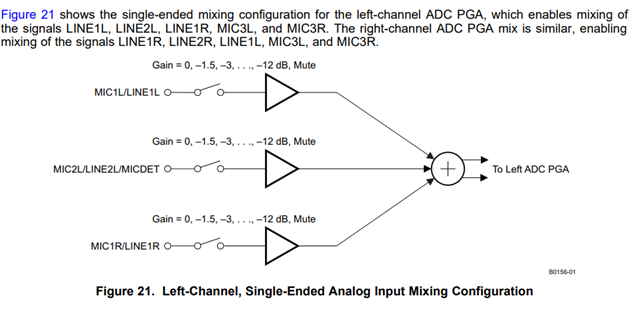

// LINE2L connected to the left ADC PGA

tlv320aic31_write(IIC_device_addr[chip_num], 17, 0x0f);

// LINE2R connected to the right ADC PGA

tlv320aic31_write(IIC_device_addr[chip_num], 18, 0xf0);

// LINE1LP is configured in single-ended mode

// LINE1L connected to the left-ADC PGA

// Left-ADC channel is powered up

tlv320aic31_write(IIC_device_addr[chip_num], 19, 0x04);

// LINE1RP is configured in single-ended mode

tlv320aic31_write(IIC_device_addr[chip_num], 21, 0xC0);

// LINE1RP is configured in single-ended mode

// LINE1R connected to the right-ADC PGA

// Right-ADC channel is powered up

tlv320aic31_write(IIC_device_addr[chip_num], 22, 0x04);

// LINE1LP is configured in single-ended mode

tlv320aic31_write(IIC_device_addr[chip_num], 24, 0xC0);

// Left DAC is powered up

// Right DAC is powered up

// HPLCOM is configured as independent single-ended output

tlv320aic31_write(IIC_device_addr[chip_num], 37, 0xe0);

// HPRCOM is configured as independent single-ended output

tlv320aic31_write(IIC_device_addr[chip_num], 38, 0x10);

// Left-DAC output selects DAC_L1 path,

// Right-DAC output selects DAC_R1 path

tlv320aic31_write(IIC_device_addr[chip_num], 41, 0x00);

// PGA_L is routed to HPLOUT

tlv320aic31_write(IIC_device_addr[chip_num], 46, 0x80);

// DAC_L1 is routed to HPLOUT

tlv320aic31_write(IIC_device_addr[chip_num], 47, 0x80);

// PGA_R is routed to HPLOUT

tlv320aic31_write(IIC_device_addr[chip_num], 49, 0x00);

// DAC_R1 is routed to HPLOUT

tlv320aic31_write(IIC_device_addr[chip_num], 50, 0x00);

// HPLOUT is not muted, HPLOUT is fully powered up

tlv320aic31_write(IIC_device_addr[chip_num], 51, 0x0f);

// PGA_L is routed to HPLCOM.

tlv320aic31_write(IIC_device_addr[chip_num], 53, 0x00);

// DAC_L1 is routed to HPLCOM

tlv320aic31_write(IIC_device_addr[chip_num], 54, 0x80);

// PGA_R is routed to HPLCOM

tlv320aic31_write(IIC_device_addr[chip_num], 56, 0x00);

// DAC_R1 is routed to HPLCOM

tlv320aic31_write(IIC_device_addr[chip_num], 57, 0x00);

// HPLCOM is not muted, HPLCOM is fully powered up

tlv320aic31_write(IIC_device_addr[chip_num], 58, 0x0f);

// PGA_L is routed to HPROUT

tlv320aic31_write(IIC_device_addr[chip_num], 60, 0x80);

// DAC_L1 is routed to HPROUT

tlv320aic31_write(IIC_device_addr[chip_num], 61, 0x80);

// PGA_R is routed to HPROUT

tlv320aic31_write(IIC_device_addr[chip_num], 63, 0x00);

// DAC_R1 is routed to HPROUT

tlv320aic31_write(IIC_device_addr[chip_num], 64, 0x00);

// HPROUT is not muted, HPROUT is fully powered up

tlv320aic31_write(IIC_device_addr[chip_num], 65, 0x0f);

// PGA_L is routed to HPRCOM

tlv320aic31_write(IIC_device_addr[chip_num], 67, 0x00);

// DAC_L1 is routed to HPRCOM

tlv320aic31_write(IIC_device_addr[chip_num], 68, 0x80);

// PGA_R is routed to HPRCOM

tlv320aic31_write(IIC_device_addr[chip_num], 70, 0x00);

// DAC_R1 is routed to HPRCOM

tlv320aic31_write(IIC_device_addr[chip_num], 71, 0x00);

// HPRCOM is not muted, HPRCOM is fully powered up

tlv320aic31_write(IIC_device_addr[chip_num], 72, 0x0f);

// The left-DAC channel is not muted.

tlv320aic31_write(IIC_device_addr[chip_num], 43, 0x80);

// The right-DAC channel is not muted

tlv320aic31_write(IIC_device_addr[chip_num], 44, 0x80);

}

不知道我的这个寄存器配置与我的硬件原理图是否匹配吗?