Part Number: TLV320ADC5120

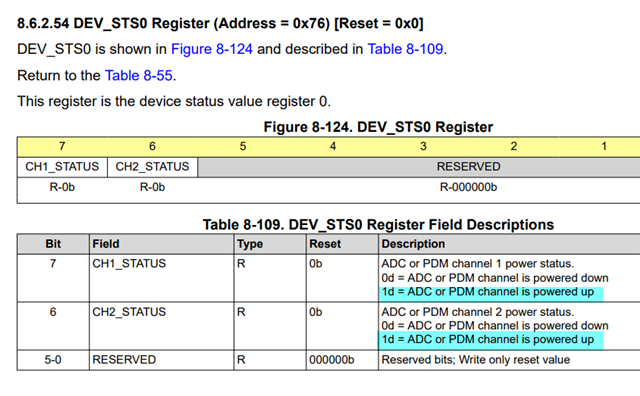

input采用2通道模拟差分输入,用I2c配置5120,BCLK和FSYNC有波形,SDOUT无输出。然后我查看DEV_STS状态寄存器发现值是c0(active mode, adc ch power down状态),但我设置了IN_CH_EN其中的ch1和ch2为enable状态。

i2c_write(PAGE_CFG_ADDRESS, PAGE_CFG_PAGE_0); i2c_write(SW_RESET_ADDRESS, SW_RESET_RESET); bflb_mtimer_delay_ms(10); i2c_write(SLEEP_CFG_ADDRESS, SLEEP_CFG_AREG_SELECT_INTERNAL | SLEEP_CFG_SLEEP_ENZ_ACTIVE); bflb_mtimer_delay_ms(10); i2c_write(ASI_CFG0_ADDRESS, ASI_CFG0_FORMAT_LJ | ASI_CFG0_WLEN_32_BITS); i2c_write(ASI_CH1_ADDRESS, ASI_CH1_CH1_SLOT_0); i2c_write(ASI_CH2_ADDRESS, ASI_CH2_CH2_SLOT_32); i2c_write(MST_CFG0_ADDRESS, MST_CFG0_MST_SLV_CFG_MASTER | MST_CFG0_FS_MODE_48_KHZ | MST_CFG0_MCLK_FREQ_SEL_12_MHZ);//mclk = 256 * freq_sample i2c_write(MST_CFG1_ADDRESS, MST_CFG1_FS_RATE_44P1_48_KHZ | MST_CFG1_FS_BCLK_RATIO_64); i2c_write(CLK_SRC_ADDRESS, CLK_SRC_DIS_PLL_SLV_CLK_SRC_BCLK | CLK_SRC_MCLK_FREQ_SEL_MODE_MCLK_FREQ_SEL | CLK_SRC_MCLK_RATIO_SEL_256);//ratio = clk / FSYNC i2c_write(GPIO_CFG0_ADDRESS, GPIO_CFG0_GPIO1_CFG_IRQ | GPIO_CFG0_GPIO1_DRV_ACTLOW_WEAKHIGH); i2c_write(GPO_CFG0_ADDRESS, GPO_CFG0_GPO1_CFG_DISABLED); i2c_write(GPI_CFG0_ADDRESS, GPI_CFG0_GPI1_CFG_DISABLED | GPI_CFG0_GPI2_CFG_DISABLED); i2c_write(INT_MASK0_ADDRESS, ~INT_MASK0_VAD_POWERUP_MASK); i2c_write(CM_TOL_CFG_ADDRESS, CM_TOL_CFG_CH1_INP_100mVpp | CM_TOL_CFG_CH2_INP_100mVpp); i2c_write(BIAS_CFG_ADDRESS, BIAS_CFG_MBIAS_VAL_VREF | BIAS_CFG_ADC_FSCALE_1VRMS); i2c_write(CH1_CFG0_ADDRESS, CH1_CFG0_INTYP_MIC | CH1_CFG0_INSRC_DIFF | CH1_CFG0_DC_AC | CH1_CFG0_IMP_2P5k | CH1_CFG0_DREEN_ENABLED); i2c_write(CH1_CFG1_ADDRESS, CH1_CFG1_GAIN_42dB); i2c_write(CH1_CFG2_ADDRESS, CH1_CFG2_DVOL_27dB); i2c_write(CH2_CFG0_ADDRESS, CH2_CFG0_INTYP_MIC | CH2_CFG0_INSRC_DIFF | CH2_CFG0_DC_AC | CH2_CFG0_IMP_2P5k | CH2_CFG0_DREEN_ENABLED); i2c_write(CH2_CFG1_ADDRESS, CH2_CFG1_GAIN_42dB); i2c_write(CH2_CFG2_ADDRESS, CH2_CFG2_DVOL_27dB); i2c_write(IN_CH_EN_ADDRESS, IN_CH_EN_CH1_ENABLED | IN_CH_EN_CH2_ENABLED | IN_CH_EN_CH3_DISABLED | IN_CH_EN_CH4_DISABLED); i2c_write(ASI_OUT_CH_EN_ADDRESS, ASI_OUT_CH_EN_CH1_ENABLED | ASI_OUT_CH_EN_CH2_ENABLED | ASI_OUT_CH_EN_CH3_TRI_STATE | ASI_OUT_CH_EN_CH4_TRI_STATE); i2c_write(PWR_CFG_ADDRESS, PWR_CFG_MICBIAS_PDZ_ON | PWR_CFG_ADC_PDZ_ON | PWR_CFG_PLL_PDZ_ON | PWR_CFG_DYN_CH_PUPD_EN_OFF | PWR_CFG_DYN_MAXCH_SEL_12 | PWR_CFG_VAD_EN_ENABLED);

询问如何才能power up以及SDO输出数据。

附上原理图

附上原理图