Part Number: TLV320AIC3109-Q1

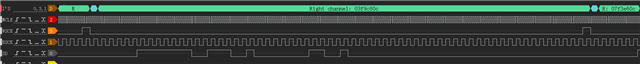

I used STM32L431 as the master to receive audio signals from TLV320. The test found that the trend of the data is right, as the input becomes larger, the output also becomes larger. But the amplitude of the signal seems to be wrong, and the duty cycle of WCLK is not 50%, but 1 bit high and 63 bits low. My configuration is I2S mode, 8K sampling, 32 bits, why does this happen and how can I troubleshoar it?tlv320aic3109-q1.pdf