Part Number: LMX2491

你好,对于这个问题我有新的疑问,你能帮我看看吗,谢谢

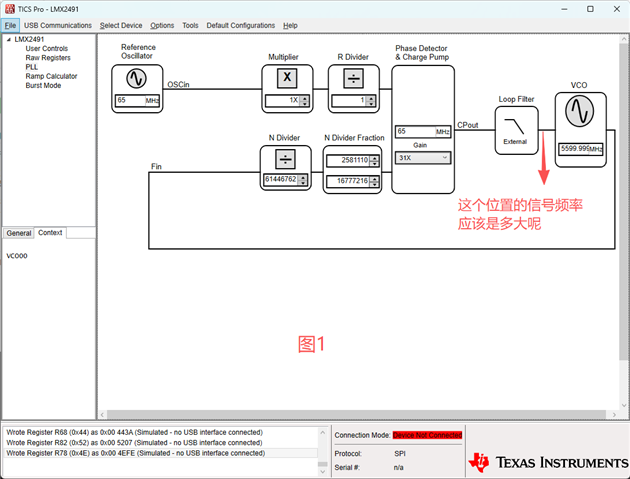

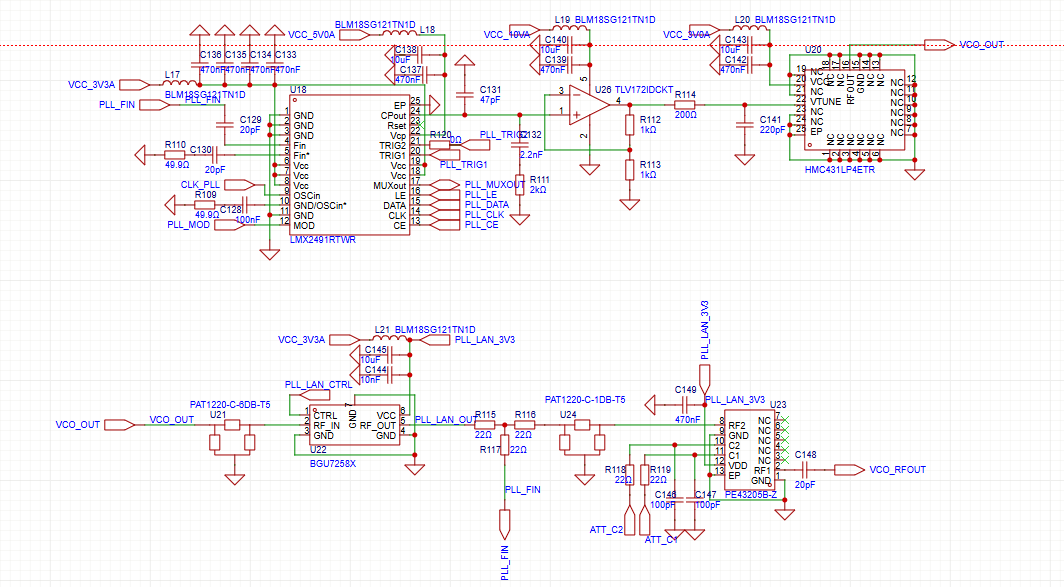

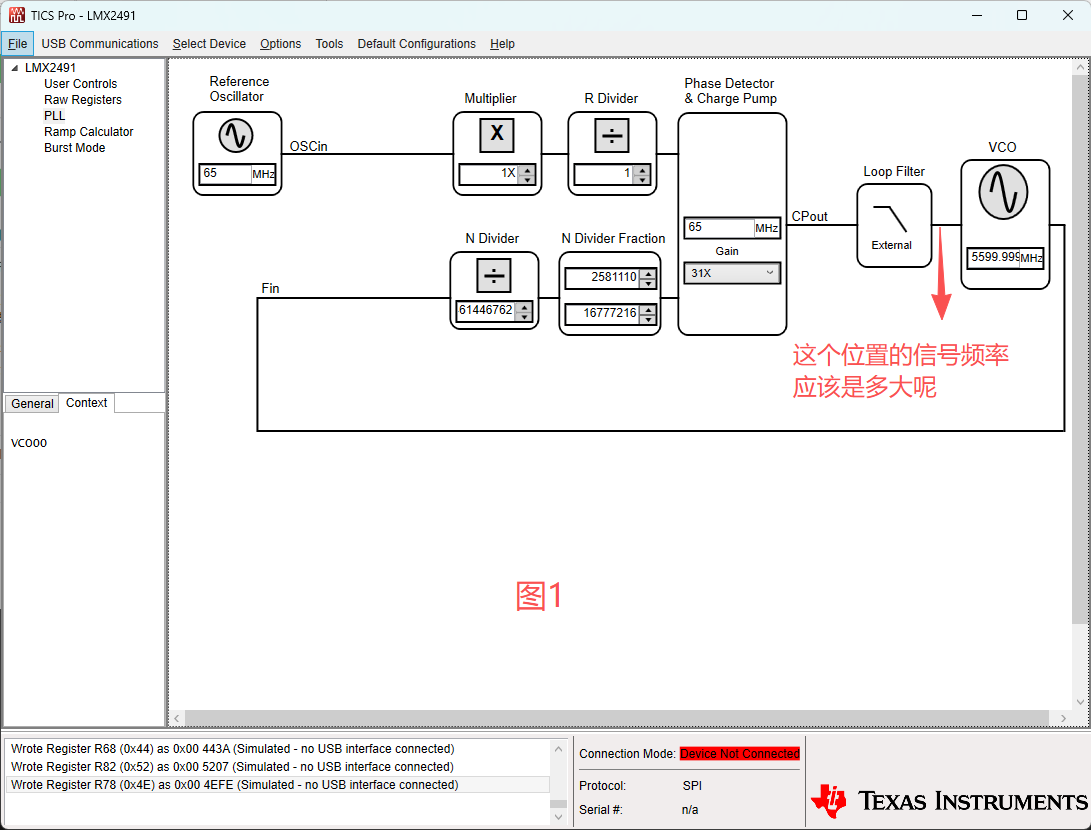

1、首先是对整个流程的解读,是不是反馈的信号经过N分频器后和经过R分频器的信号不断地进行相位比较,在cpout口输出一个电流信号,电流信号经过外部的环路滤波就是变成电压信号,相应的电压斜坡信号再经过外部的vco得到对应的频率斜坡信号(我这个例子中是5.5~6.1GHz的线性调频信号)

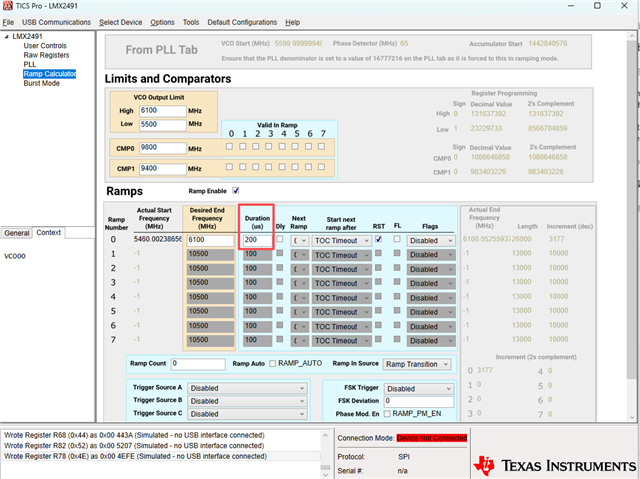

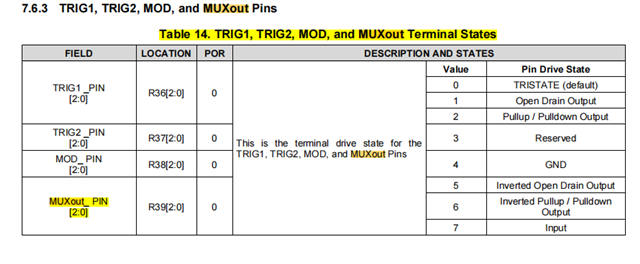

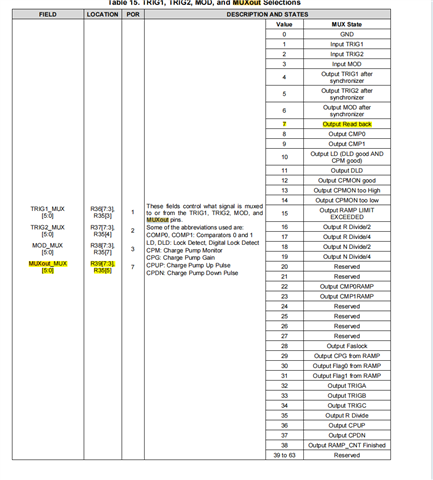

2、对于寄存器信息配置部分,下面的图1会对我的斜坡波形(图2)有所影响吗,因为我的目的是在vco的输出部分得到一个5.5~6.1GHz的信号,而不是单频信号。然后图1环路滤波器的末端应该是得到一个通过200微秒计算得到的5kHz的电压斜坡波形是吗,还是说是一个65MHz相关的信号

3、我像图2那样配置是在cpout就输出一个线性调频波还是在外部vco后面才输出线性调频波

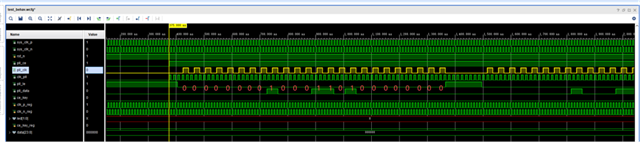

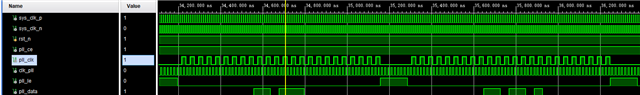

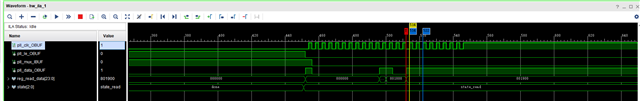

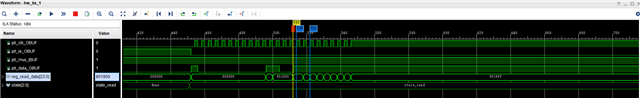

4、我是通过spi来通信的,vivado仿真的波形如图,写24个数据后就缓冲,再写24个数据,这有什么错误吗

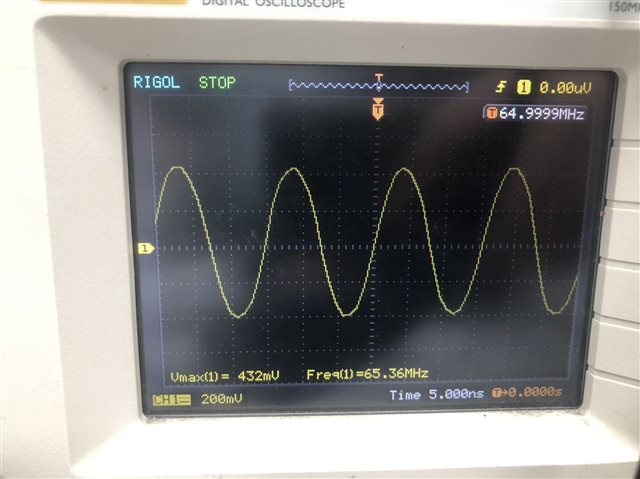

5、如果我想要验证,有什么方法吗,因为我现在示波器测出来的有点怪

我的理解是这个部分配置了N分频器和R分频器的信息,想得到5.5~6.1GHz线性调频信号要使能斜坡波形,这正确吗

我的理解是这个部分配置了N分频器和R分频器的信息,想得到5.5~6.1GHz线性调频信号要使能斜坡波形,这正确吗

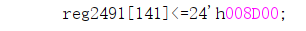

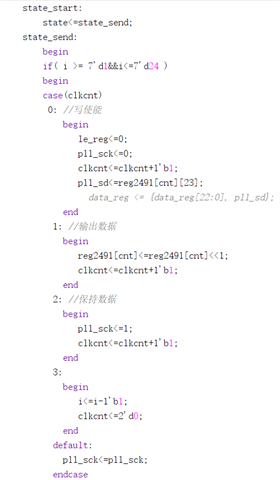

这个是我写数据的代码,基准的clk是100MHz的,也就是说pll_sck是25MHz的

这个是我写数据的代码,基准的clk是100MHz的,也就是说pll_sck是25MHz的