Part Number: CDCM7005

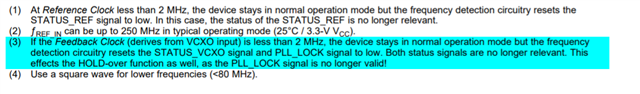

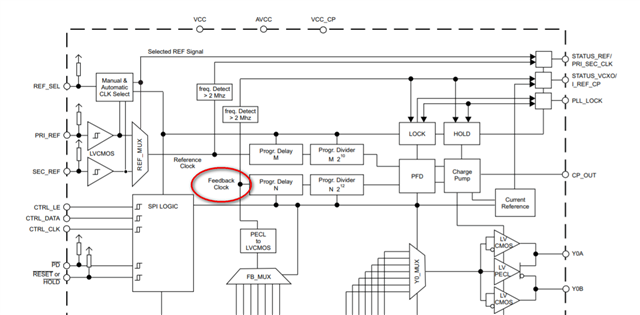

原理图接法:

VCO指标:

输出频率:384MHz

输出功率:1.5~4.5dBm

调谐电压0.5~2.5V

压控灵敏度:3-6MHz/V

PLL设置:

输出时钟:384MHz,96MHz,24MHz

参考时钟:100MHz

问题:六块板卡有两块的板卡的CDCM7005芯片,STATUS_VCO状态指示管脚,在低温-10度时,STATUS_VCO状态指示异常,锁定指示也异常,但测试芯片的输出时钟384MHz,96MHz,24MHz无问题,证明锁相环锁定正常,仅状态指示异常。常温无任何问题。

改环路带宽为100K,问题仍然存在。

手册上查不到,STATUS_VCO状态指示的内部电路,不清楚问题出在哪?

VCO为单端输出,接到锁相环芯片的VCXO_IN+管脚,datasheet中并没有单端输入的接法说明,请问这种接法对么?