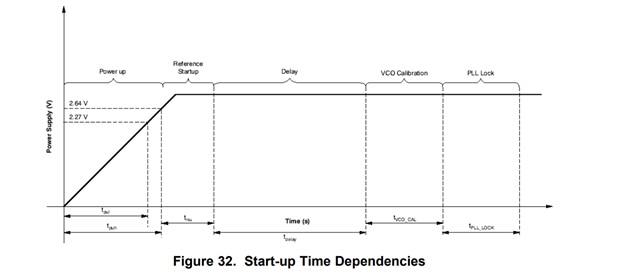

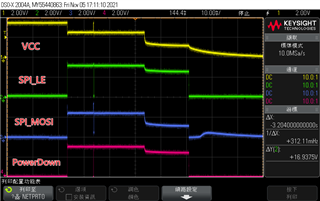

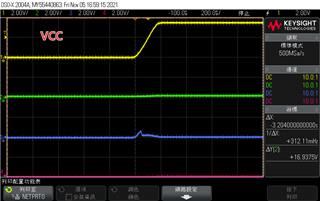

Hello, I want to program CDCE62005 by myself through SPI, but everytime when I set SPI_LE to HIGH and do rising edge to Power_Down, I just hava 20ms to access device registers, but I need to do 「Copy RAM to EEPROM – Unlock」 it have to wait at least 50ms, when after 20ms the VCC will pull down by IC, Please help.

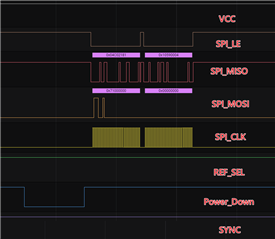

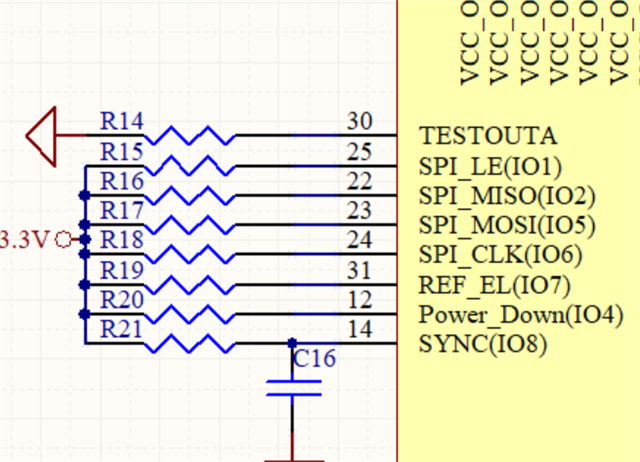

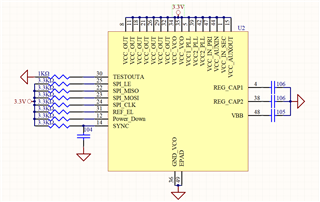

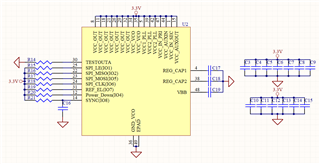

Here is my circuit.

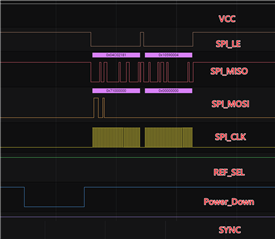

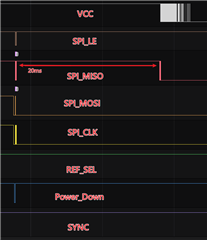

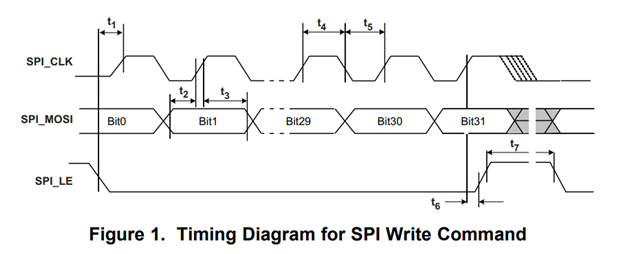

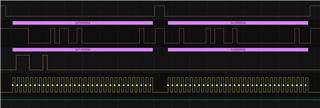

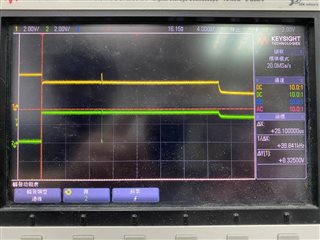

Here is the SPI Wave