Part Number: CDCE813-Q1

你好

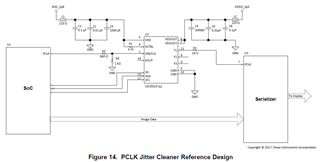

我设计的电路和下图一样,SOC 输出24.567MHz的1.8V MCLK 给到DSP, DSP 要求MCLK 为3.3V jitter 低于100ps ,SOC输出 jitter 大约在500ps左右,单输入单输出。

那么CDCE813-Q1 是否可以满足要求?如果使用 CDCE813R02TPWRQ1,I2C是否可以不接到SOC,不做控制? 感谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: CDCE813-Q1

你好

我设计的电路和下图一样,SOC 输出24.567MHz的1.8V MCLK 给到DSP, DSP 要求MCLK 为3.3V jitter 低于100ps ,SOC输出 jitter 大约在500ps左右,单输入单输出。

那么CDCE813-Q1 是否可以满足要求?如果使用 CDCE813R02TPWRQ1,I2C是否可以不接到SOC,不做控制? 感谢

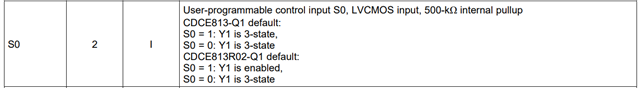

您好,CDCE813-Q1的默认输出都是disable的,所以只能通过I2C enable output。 它和CDCE813R02的区别就在于默认配置下,只有Y1 输出enable。所以如果只需要一路输出,使用CDCE813R02 可以不使用Soc的I2C 对其进行配置,但是如果也需要其他几路的输出,则需要I2C控制。

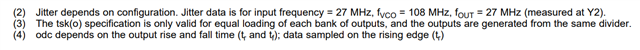

对于输出jitter是否能低于100ps, 需要实际配置和测试,datasheet中给出的cycle to cycle和peak to peak的jitter值是在fin=27Mhz,fvco=108Mhz的条件下测试的,并且jitter的性能和配置是有关的,datasheet Page7有下面这个备注,由于PLL频率不同,分频系数的配置不同,所以针对不同的应用,内部环路滤波器会自动进行调节到最高性能和最优jitter。

你好

CDCE813R02可以不使用Soc的I2C 对其进行配置 ,那么他的输出和输入是如何对应的呢?是1:1的还是有倍频的? 感谢

宏伟

默认配置就是个buffer的功能,分频系数divider=1,输入输出频率一样,并且只有Y1输出enable, 其他几路默认输出disable,如果需要输出的话则通过I2C enable。

你好

这个buffer 的功能 可以实现降低 jitter的目的么?

宏伟

CDCE813R02默认的配置 PLL 是使能的,还是下面那条线bypass 的?

我使用上是不倍频,仅仅使用PLL 来去jitter,CDCE813R02默认的配置是否正好合适呢? 感谢

这个buffer 的功能 可以实现降低 jitter的目的么?

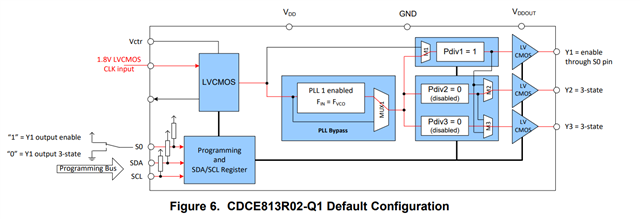

输出和输入频率相同,采用默认配置,实现的是对输入信号的jitter cleaner功能,框图中红线路径就是默认配置的路径。

默认配置是PLLenable的,并且使用jitter cleaner功能的话,也是需要PLL enable的。

但是有一个问题,默认配置下,fin=fVCO,而VCO的频率范围是70Mhz~230Mhz,所以如果输入24.567Mhz的话,不在70Mhz范围内,所以只使用默认配置还是不可以的。

你好

那就是I2C一定要接上了。对我来说也没啥区别了。

那么这2个IC哪个更通用?使用的人更多呢? 我希望选一个交期好一点的 多谢

如果说这两款选择哪一款,我认为都可以,唯一的差别就是在于CDCE813R02默认的Y1是输出enable的,而CDCE813 输出都是disable,只能通过I2C进行配置。但是既然都需要I2C了,这两款也就没什么区别了。从客户咨询的角度来看,可能CDCE813更多一些吧。

关于交期的话,建议是直接联系我们的客户支持部分,关于购买事宜都可以联系他们: