Part Number: LMK03200

时钟配置问题,125M输入配置成125M的输出。

配置focin=125M,PLL_N=10,VCO_DIVIDER=5,PLL_R=5,CLKOUTX_DIVIDER=1,输出135M左右,是我配置参数有问题吗?怎么修改比较好?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

配置顺序如下

LMK_GOE <= '0';

LMK03200_SPI_data <= x"8000000";

LMK_ADDR_wr <= x"0";

LMK03200_SPI_data <= x"1003010";

LMK_ADDR_wr <= x"0";

LMK03200_SPI_data <= x"0003010";

LMK_ADDR_wr <= x"1";

LMK03200_SPI_data <= x"0003010";

LMK_ADDR_wr <= x"3";

LMK03200_SPI_data <= x"0003010";

LMK_ADDR_wr <= x"4";

LMK03200_SPI_data <= x"0003010";

LMK_ADDR_wr <= x"7";

LMK03200_SPI_data <= x"0003010";

LMK_ADDR_wr <= x"2";

LMK03200_SPI_data <= x"0003010";

LMK_ADDR_wr <= x"5";

LMK03200_SPI_data <= x"0003010";

LMK_ADDR_wr <= x"6";

LMK03200_SPI_data <= x"1000090";

LMK_ADDR_wr <= x"8";

LMK03200_SPI_data <= x"0082000";

LMK_ADDR_wr <= x"B";

LMK03200_SPI_data <= x"029F400";

LMK_ADDR_wr <= x"D";

LMK03200_SPI_data <= x"0830040";

LMK_ADDR_wr <= x"E";

LMK03200_SPI_data <= x"10000A0";

LMK_ADDR_wr <= x"F";

LMK_GOE <= '1';

LMK03200_SPI_data <= x"1803010";

LMK_ADDR_wr <= x"0";

LMK03200_SPI_data <= x"10000A0";

LMK_ADDR_wr <= x"F";

您好,建议使用TICSPro这个软件帮助进行配置。

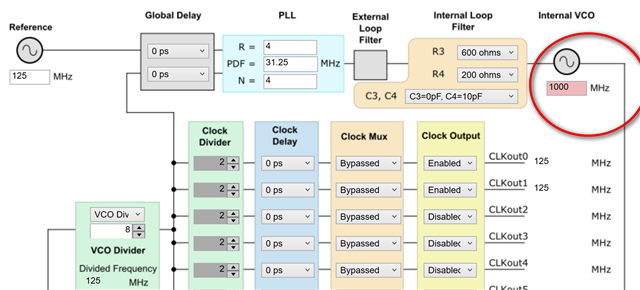

focin=125M,PLL_N=10,VCO_DIVIDER=5,PLL_R=5,CLKOUTX_DIVIDER=1,

这个配置下的VCO频率是多少? 注意VCO 频率范围为1125Mhz~1296Mhz的范围。我刚试了下,如果输出125MHz,VCO=1000Mhz小于1185Mhz,所以是不允许的。

您好,抱歉回复晚了,寄存器配置和TICSPro的寄存器配置相同,因此不是配置的问题。

我想问下,PLL是否已经lock?按照TICSPro的配置,PLL应该是lock的。

但是输出频率出现频偏,我想和参考时钟应该是有关系的,如果参考时钟有频偏,则会导致输出也有频偏。

方便更换其他的参考时钟源再试试吗?尽量使用jitter 稍低,频偏也较低的参考时钟。

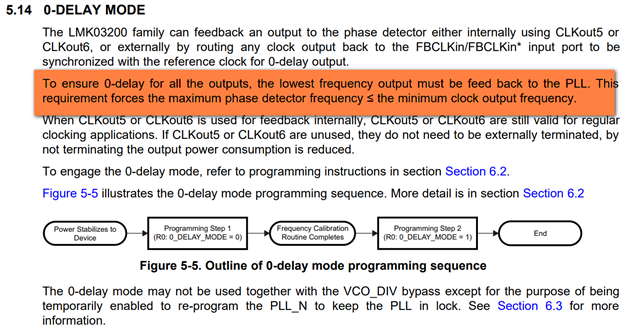

抱歉,回复晚了。 如果开启0 delay mode的话,建议是参考6.2 Recommended Programing Sequence, with 0-Delay Mode的配置顺序。

另外, 0 delay mode话,输出可以通过外部反馈到相位检测器,而CLKOUT5和CLKOUT6内部输出已经反馈到phase detector。所以其他几路输出如果需要0 delay mode话可以将输出反馈到FBCLKIN。

如果要使得所有输出0 delay 的话,需要最小输出频率必须反馈到PLL,这就需要最大相位检测器的频率<=最小输出频率,如下描述。

所以我想上述原因是关闭0 delay mode的话,可以正常输出的原因,因为除了CLKOUT5和CLKOUT6,其他通道没有外接反馈,是无法达到0 delay mode的。

您可以按照6.2.1 0-Delay Mode Example 1和6.2.2 0-Delay Mode Example 2,分别对CLKOUT5进行0 delay mode的配置,和CLKOUT6进行0 delay mode的配置,看这两个通道是否能准确输出。