Part Number: LMK1C1104

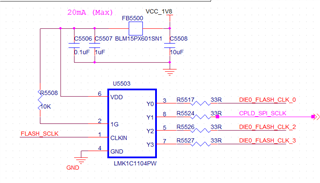

您好,我们CLKIN的输入是通过软件指令手动输入的,可以保证是在VDD稳定后大于3ms才有CLKIN产生的,下图是SCH,VCC_1V8很早就已上电并上拉1G使能;

请问还会有别的点可尝试debug么? 谢谢。

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.