使能sysref后,logiclk将会出现问题,咨询下是否有什么注意的要点或者解决方案

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,建议将您的问题描述的稍微详细些哈,SYSREF enable之后,LOGICLK具体出现了什么问题?

我们使用的是plmx1204,在使用过程中发现,如果不使能sysref即寄存器R15[7]为0,可以得到想要频率的logiclk,但是使能了sysref即寄存器R15[7]为1,logiclk从频谱仪来看就会出现很多频率点的时钟,是否是plmx1204和lmx1204的寄存器不一样吗,还是什么原因造成的

您现在使用的是PLMX1204遇到的SYSREFOUT在sysref使能了之后不能输出的这个问题是吗?PLMX1204是TI的时钟芯片吗?我在官网没找到这个型号。

您好,PLMX的评估版本,抱歉我这边没有任何它的资料呢。 所以也无法辨别它和LMX1204的差异在哪儿。

我疑惑的是,您在哪儿购买的PLMX的版本?为什么不直接购买LMX1204呢?

您的这个问题我建议是使用LMX1204,看看是否会出现类似的问题呢。

好的,抱歉, 那是我理解错了,看到您上面的帖子关于“ plmx1204和lmx1204的寄存器是否有差异" , 以为是PLMX1204的芯片型号.而我这边又查不到这个型号,所以和您确认了下。

那我会针对LMX1204的这个现象看一下您的问题,给您带来不便非常抱歉。

sysrefout没有输出,查看下寄存器R17的bit [1:0]SYSREF_MODE 建议配置成0x0,continuous mode。

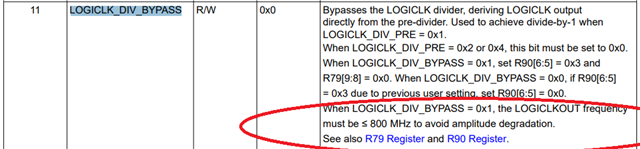

另外,就是LOGICLK_DIV_BYPASS 这bit您配置的是什么?注意LOGICLKOUT的频率要小于800Mhz避免幅值降低。所以您前面提到Logiout输出幅值降低,是不是频率超过800Mhz的原因呢?

您使用的不是最新版本的TICSPro,我看了下我的TICSpro的版本是1.7.5.7. 您先下载最新版本的TICSPro对其进行寄存器配置看看能解决问题吗?

https://www.ti.com.cn/tool/cn/TICSPRO-SW?keyMatch=TICS%20PRO%20SOFTWARE

如果仍不能,将您的TICSpro配置的截图附上,以及LOGIOUT间隔频率的波形附上,我这边去确认这个问题。

恩我看了下TICSpro的配置没什么问题。

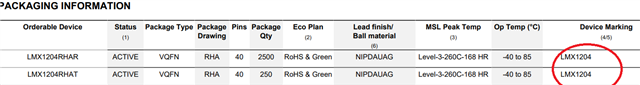

另外,我看了下LMX1204的顶端标识确实只有LMX1204.我看您评估版的LMX1204的顶端标识为PLMX,所以我需要和美国工程师确认下。 给您带来不便非常抱歉,如收到回复,我会理解通知给您。

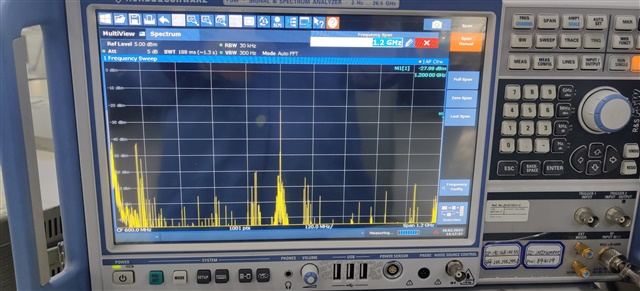

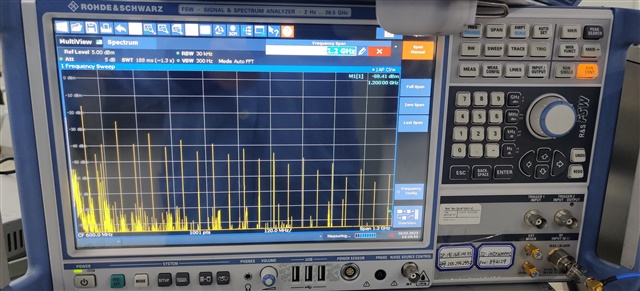

图一是没有使能sysref_en时logiclk输出现象,可以得到想要的600mhz的输出频点(旁边的干扰是因为没有接地,可以忽略),第二张图是使能了sysref_en时,logiclk输出现象,配置是按照之前发的图片中的配置,两个唯一不同的是sysref_en寄存器R15[7],sysref模式为continuous。请问下造成这个的原因是什么,还有就是lmx1204的评估版本和正式版的寄存器存在什么差别吗,目前官网上只能下载正式版的寄存器手册,请问有评估版的寄存器手册吗,谢谢

PLMX的寄存器手册或者其他任何资料我这边也没有,关于这个问题,我已经向美国那边反应了,等待他们的回复。

抱歉,因为我们每天有很多客户咨询技术问题,也理解客户项目都比较急, 所以我们会尽快给客户回答,那针对您的问题,我这边只要收到美国的回复,会立即给您答复的。 因为美国和我们有时差,通常情况下明天我会收到答复,然后我会反馈给您,如果解决不了 我会再反馈到美国那边。

您好,我这边有收到回复,美国工程师并没有针对此技术问题给出回答,他的意思是PLMX是我们的原型芯片,如果您购买的板子芯片是PLMX,联系sales去改成最终我们LMX1204的版本去使用。

您好,我这边已经收到回复:美国那边的意思是如果开发板的购买周期很长,建议是您替换LMX1204的芯片。 据他所了解的,最终版本的芯片和最原始的是有些差异的。