Part Number: LMK05318BEVM

Other Parts Discussed in Thread: LMK03318, CDCE6214, LMK05318B

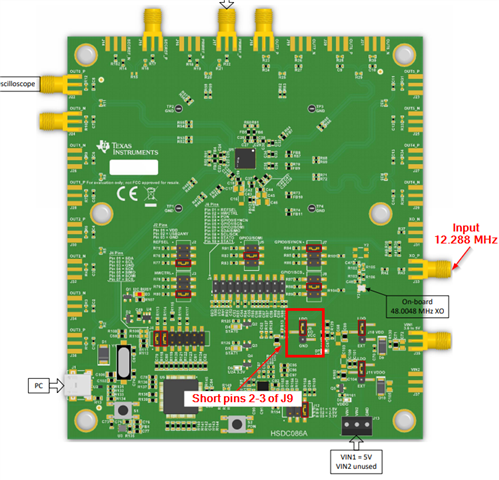

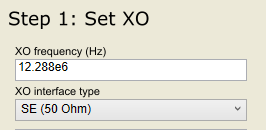

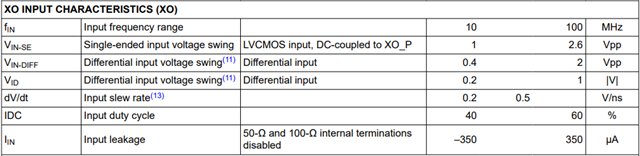

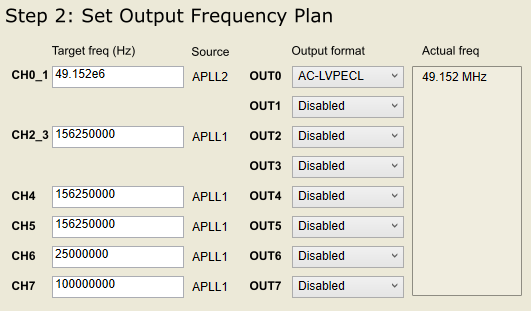

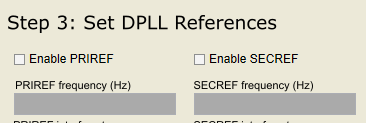

我们使用开发板,想实现输入时钟和输出时钟相位同步的功能,输入和输出时钟都是LVCMOS电平,一路输入时钟12.288M,一路输出时钟49.152M。

要求输入12.288M时钟相位变化时,输出时钟的相位也尽快调整,与输入时钟相位对齐。我们尝试了好多配置,都无法实现。除了配置wizard的内容之外,是否还需要其他配置?advance的内容如何配置?是否要选择ZDM功能?能帮我们提供一个适合的配置吗?