Part Number: LMK00725

Hi:

请教一个问题,当LMK00725的输入为LVPECL电平时,由于芯片输入管脚内部存在51KOhm上下拉,那在芯片外部是否还需要增加上下拉偏置电阻呢?

我目前参考的是手册中的典型应用电路(Datasheet Figure19)进行设计的,100R端接,前端LVPECL输出180R下拉,如下图1,没有预留上下拉偏置电阻。

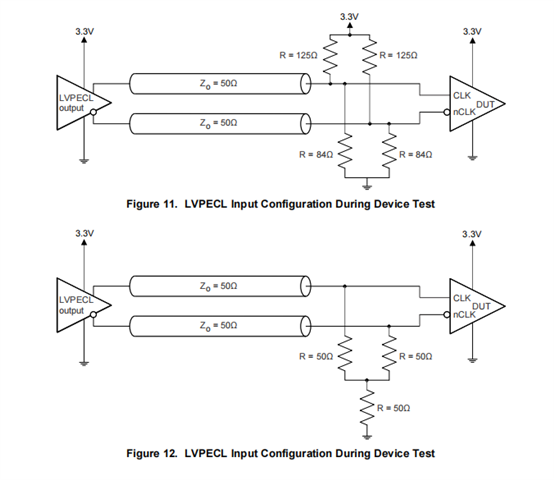

但检查手册中的Figure11与Figure12,如下图,输入的接法和上图Figure19是不一致的,搞得我有点混乱。。。

确认下手册中这三张图对应的三种接法模式是否都可以工作呢?

请帮忙解答下,感谢!