Part Number: DAC3482

请教一个问题;

我在使用DAC3482时,从fpga发送DAC的数据会丢掉一部分,找不到原因和解决办法,希望有人能给出解决的办法

我做了一块电路板,DAC为DAC3482IRKD,DAC通过LVDS接口连接到FPGA。

1 DAC配置

DACCLK 625 MHz(外部、无内插,NCO禁用)

DATACLK 312.5 MHz

LVDS BUS输入模式 Word wide

插值滤波器 *1

FIFO同步 Sif同步

锁相环 By Pass

2 数据输入

正弦波(DACI和DACQ都是正弦波),LVDS信号,由FPGA产生

3 寄存器设置

寄存器 设置值

0x00 0x0098

0x01 0x004E

0x02 0x8082

0x03 0xA000

0x07 0x0100

0x09 0x8000

0x18 0x2008

0x19 0x0440

0x1A 0x0020

0x1B 0x0800

0x1F 0x818C

0x20 0x8800

0x1F 0x818E

0x1F 0x818C

0x20 0x0000

0x24 0xE000

0x03 0xA001

4 结果

- Alarm FIFO FIFO pointer collision

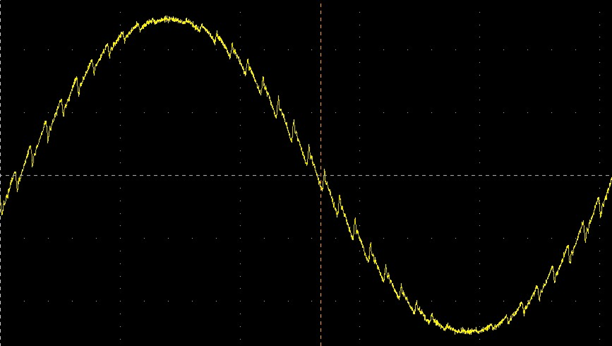

- 输出波形失真,DACI和DACQ输出波形上有锯齿状毛刺,将插值滤波器设置为2X(interpolation factor)时,波形依旧,Alarm FIFO有告警

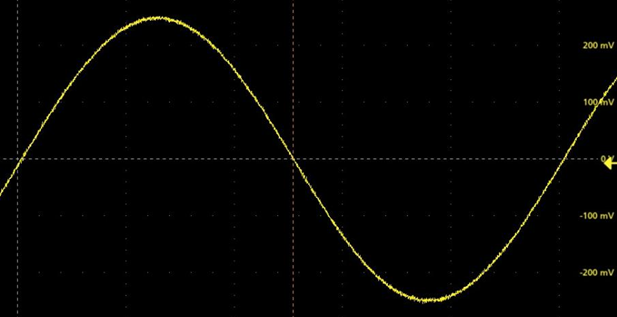

- 将插值滤波器设置为4X(interpolation factor)时,Alarm FIFO不再告警,DACI和DACQ输出正常的正弦波

-

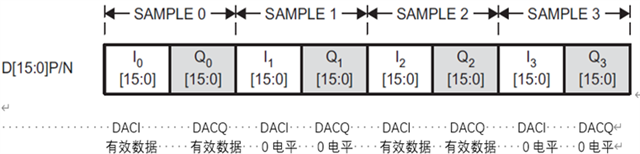

保持设置不变的前提下,在fpga中将正弦波数据做出调整,DACI和DACQ的数据都为1个正弦波有效数据+1个0电平,DACI和DACQ能够输出正常的正弦波

- 将DACI和DACQ的数据数据调整为1个0电平+1个正弦波有效数据,DACI和DACQ都输出0电平

- 从结果看,DAC把fpga过来数据中的sample1、sample3、sample5、sample7…等都丢掉了,丢失波形数据是不能接受的