Part Number: AFE58JD32

Dear TI experts,

We have encountered a problem while using the AFE58JD32 device.

We are using the JESD204B interface of AFE58JD32 (4 lane mode, F=6, K=3)

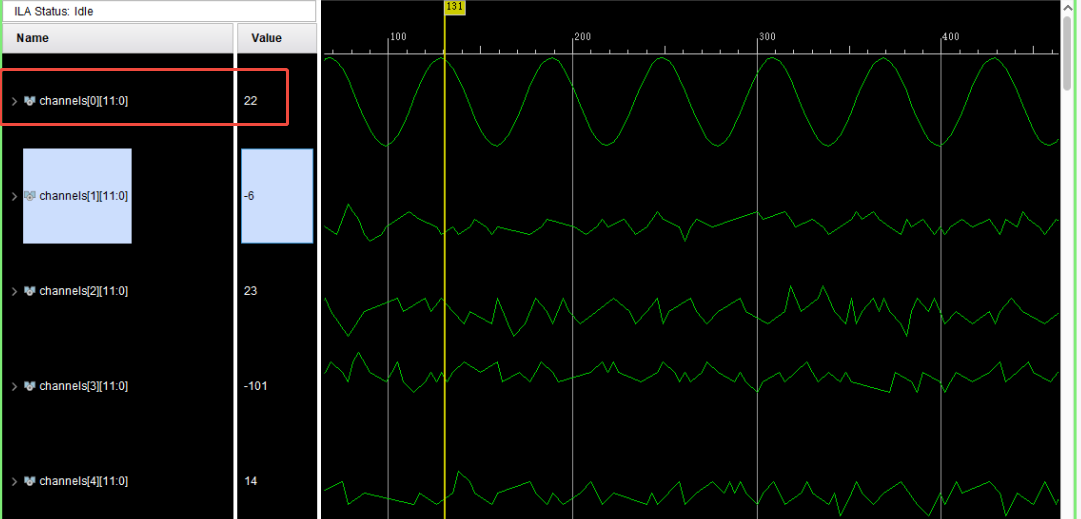

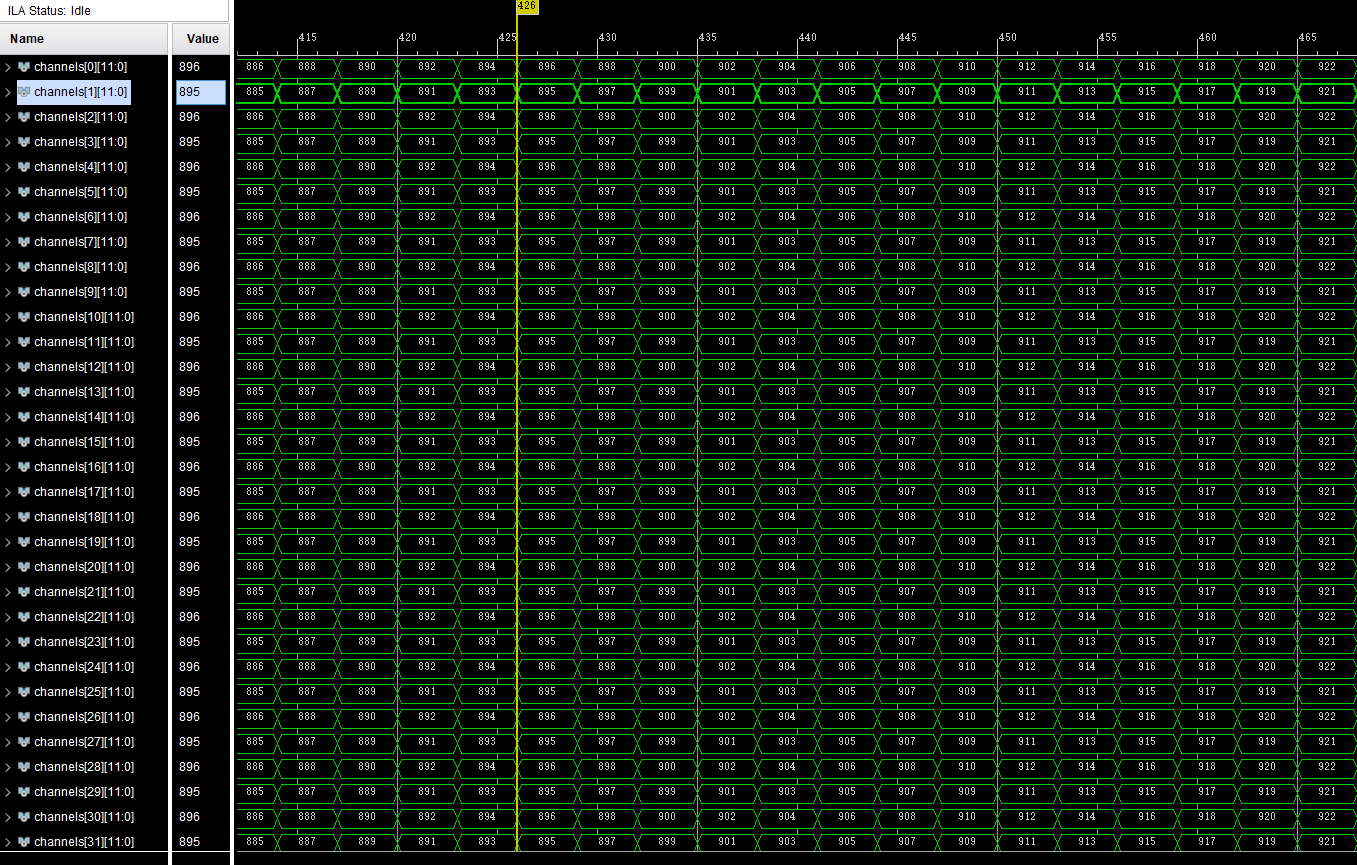

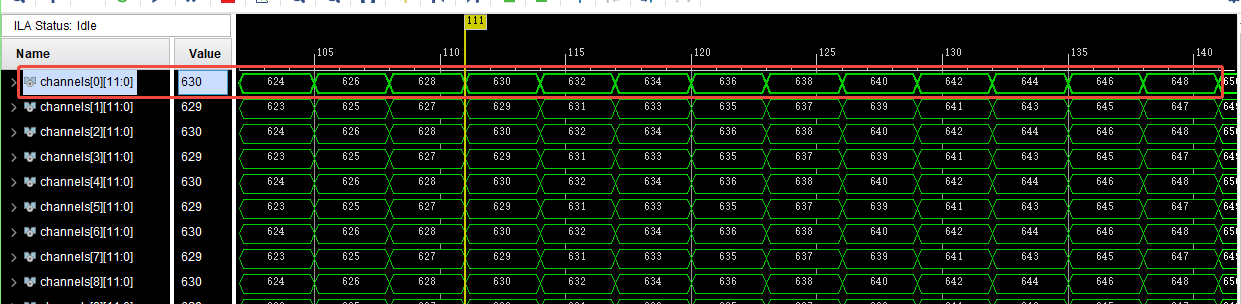

We set the AFE58JD32 to the ramp mode. Then, the odd channels and even channels differ by 1, and each channel increases by 2 in sequence.(As shown in the figure below)

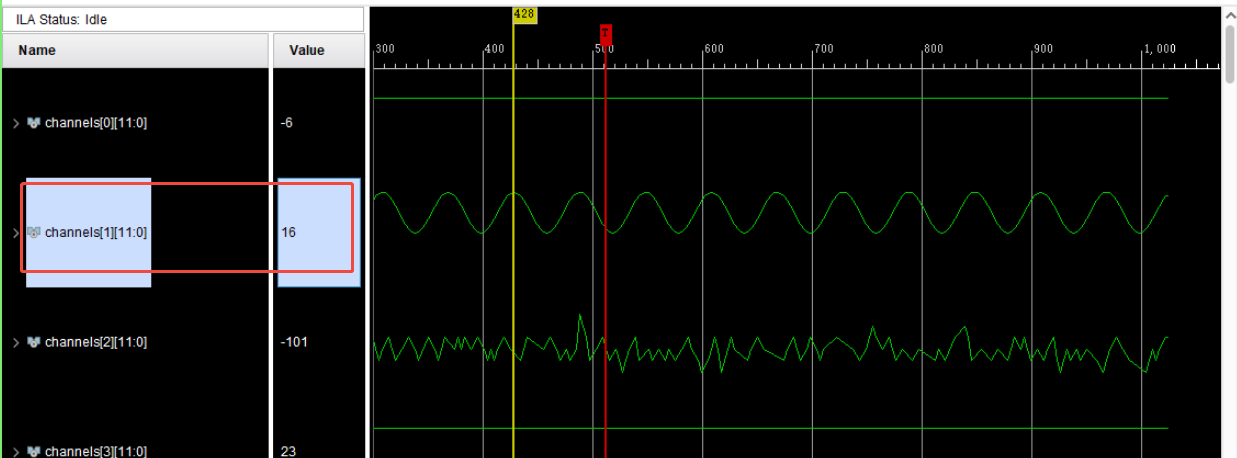

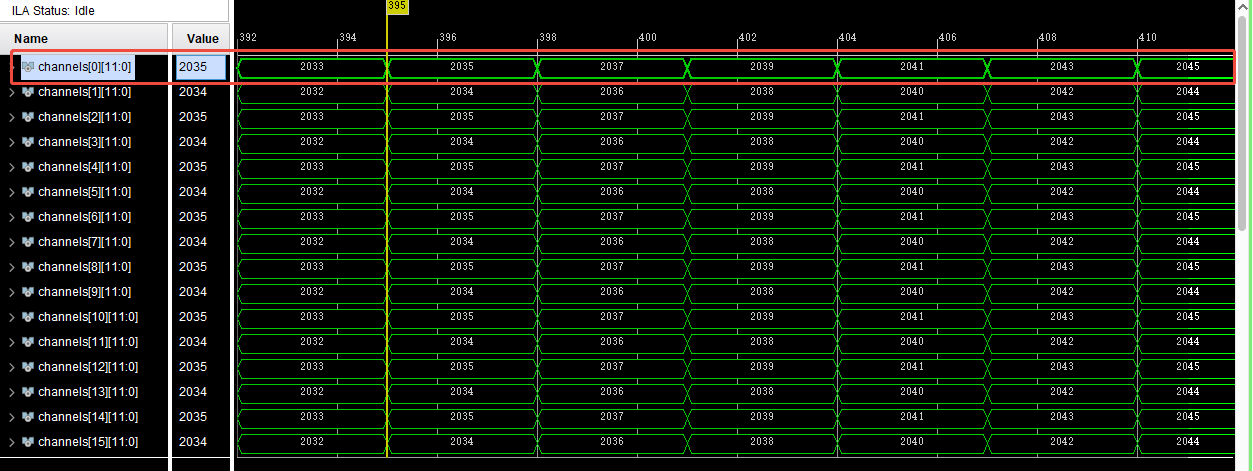

However, whenever we power on the device again, if we configure the AFE58JD32 to the ramp mode, we will observe the following situation

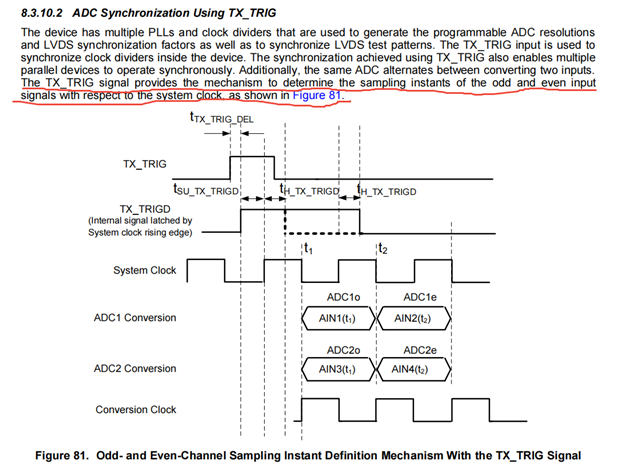

After this power-on operation, the value of channels0 is an odd number. On the next power-on, the value of channels0 will be an even number. This means that after powering on, the value of channel 0 could be an odd number or an even number.

How should I go about solving this problem?

thank you