Part Number: ADS1018

Other Parts Discussed in Thread: ADS1118

Hi 您好。

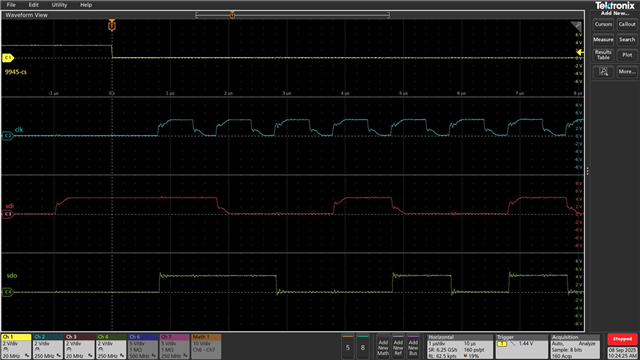

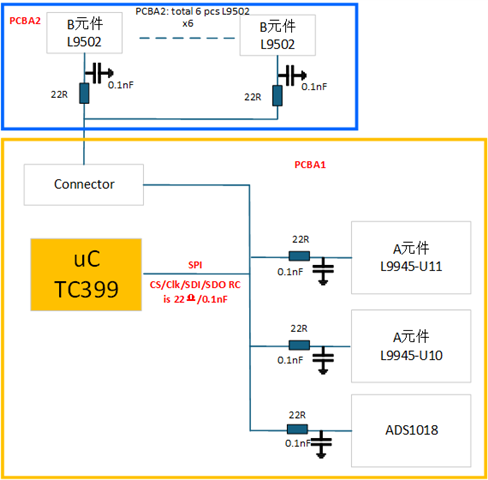

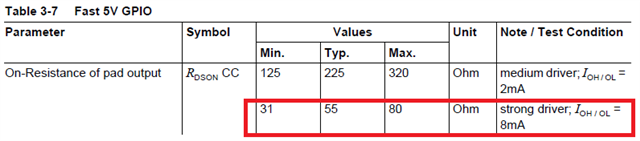

背景:MCU的SPI总线带有9个从设备,负载分别是:1个ADS1018、2个A元件、6个B元件,其中ADS1018的SPI速率是200kbps, A元件SPI速率是1Mbps,C元件SPI速率是100kbps。SPI波形有振铃,ADS1018和A元件的SPI通信有时候会报错。

请求支持:是否可提供SPI多设备总线设计资料,用于评估MCU是否可驱动多个SPI从设备,SPI从设备数量是否合理,从设备的容性负载是否合理等?

谢谢。