Part Number: DAC38RF80EVM

Other Parts Discussed in Thread: LMK04828, DAC38RF80, DAC38RF82

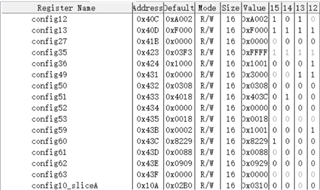

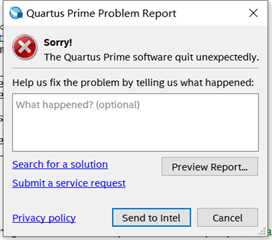

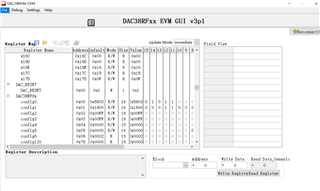

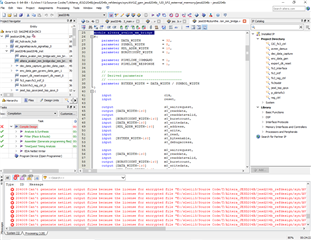

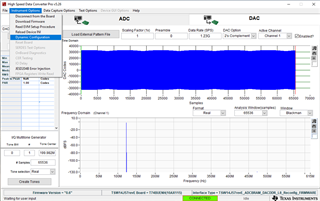

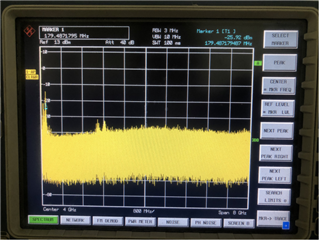

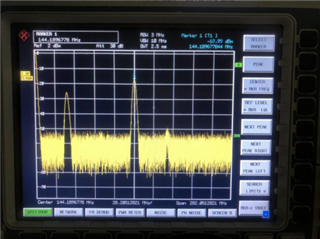

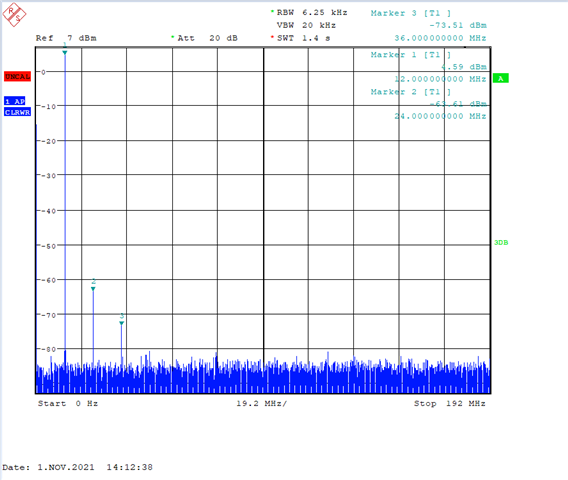

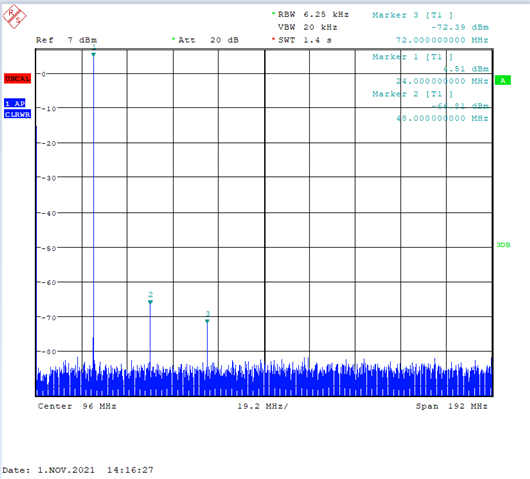

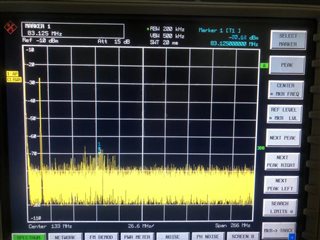

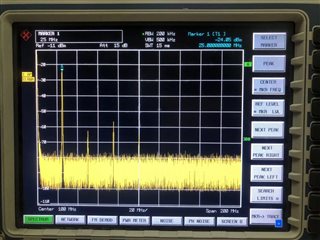

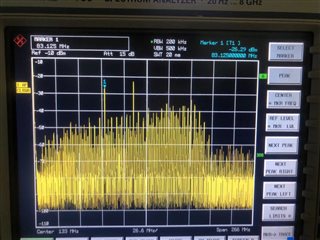

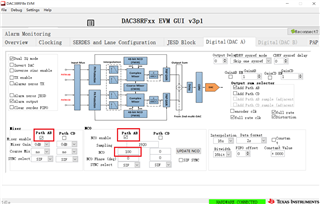

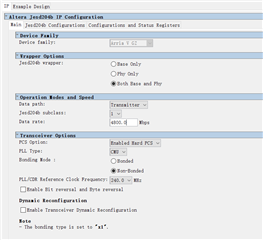

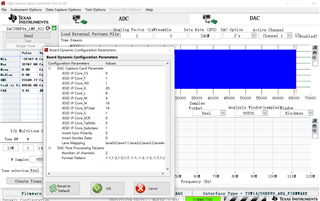

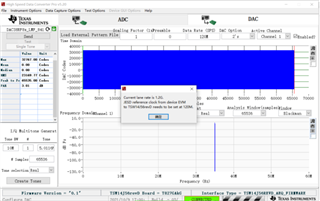

在TSW14J56板子与DAC38RF80EVM联调的中,可以通过外部时钟和DAC_PLL模式,根据文档设定的参数 6144MHz可以调试出波形,但是对于外部时钟模式,当改变6144M就时钟就始终无法调试出波形,且软件报错如下。

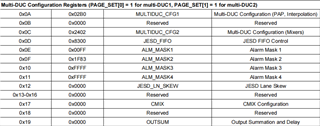

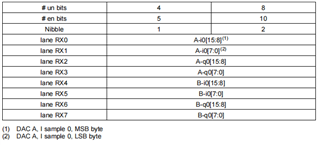

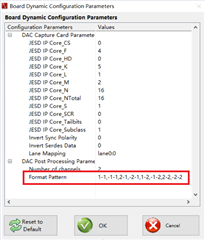

看这个报错,可能是由于射频采样率改变后,JESD的参考时钟也要改变。但是,一直没法在软件中找到改变时钟的办法。请问,这里的JESD参考时钟如何调整?