如题,我设置的前台校准,FG—DONE没有拉高,2C1寄存器0000_0010,208寄存器0111_1100。采样数据在FPGA端随机性出现错点。请问是什么原因?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

如题,我设置的前台校准,FG—DONE没有拉高,2C1寄存器0000_0010,208寄存器0111_1100。采样数据在FPGA端随机性出现错点。请问是什么原因?

您好,FG校验应该在初始化过程中完成的,FG_done一直没有拉高。建议先检查下初始化顺序,参考数据手册的8.3部分的初始化顺序:

8.3 Initialization Set Up The device and JESD204 interface require a specific startup and alignment sequence. The general order of that sequence is listed in the following steps.

1. Power-up or reset the device.

2. Apply a stable device CLK signal at the desired frequency.

3. Program JESD_EN = 0 to stop the JESD204B state machine and allow setting changes.

4. Program CAL_EN = 0 to stop the calibration state machine and allow setting changes.

5. Program the desired JMODE.

6. Program the desired KM1 value. KM1 = K–1.

7. Program SYNC_SEL as needed. Choose SYNCSE or timestamp differential inputs.

8. Configure device calibration settings as desired. Select foreground or background calibration modes and offset calibration as needed.

9. Program CAL_EN = 1 to enable the calibration state machine.

10. Enable overrange via OVR_EN and adjust settings if desired.

11. Program JESD_EN = 1 to re-start the JESD204B state machine and allow the link to restart.

12. The JESD204B interface operates in response to the applied SYNC signal from the receiver.

13. Program CAL_SOFT_TRIG = 0. 14. Program CAL_SOFT_TRIG = 1 to initiate a calibration.

您好,请问校准功能校准的是那一部分?如果只是采样部分的话,我觉得那跟我的情况关系不大。因为我采用ramp模式,已经抛开了采样部分,直接AD产生的数据,在FPGA端抓取的数据还是有错点

您好,抱歉回复晚了,ramp 模式是指的Ramp Test Pattern 是吗?

是否采用GUI配置的?如果是的话,建议将GUI的配置截图附上看下。

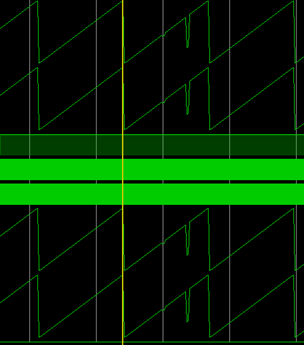

JESD204B ramp模式由每个输出数据通道的八位元值组成,当转换为JMODE0,1,1或3的12bit样本时,不会产生非常有用的数据 模式,如果想查看12bit的测试模式,建议使用JESD204Bshort transmission test mode。参考FIgure 40所示。