Part Number: ADC3664EVM

Other Parts Discussed in Thread: ADC3664

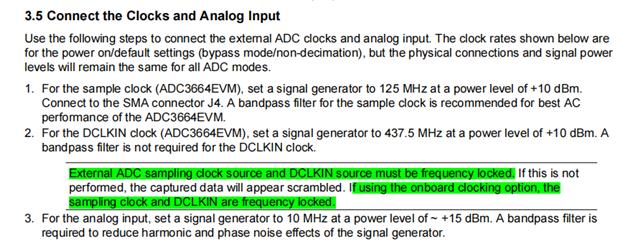

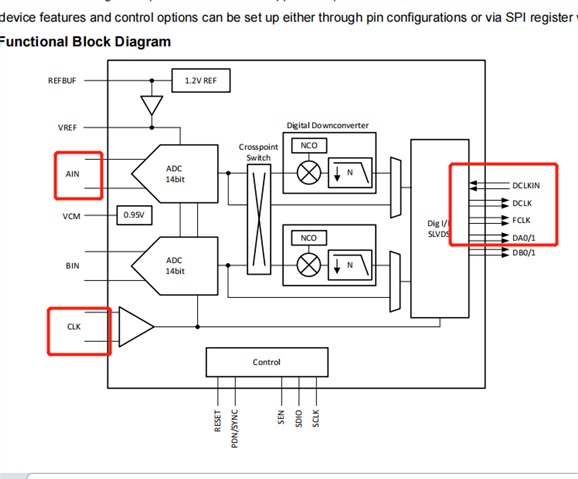

你好,关于adc3664evm板子,我们这边提供了clk dclkin以及ain,板子能够正常返回dclk,但是返回的fclk一直是高电平,且da0一直拉高是怎么回事?

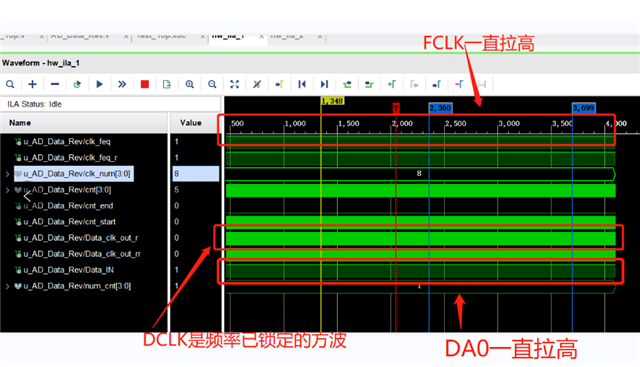

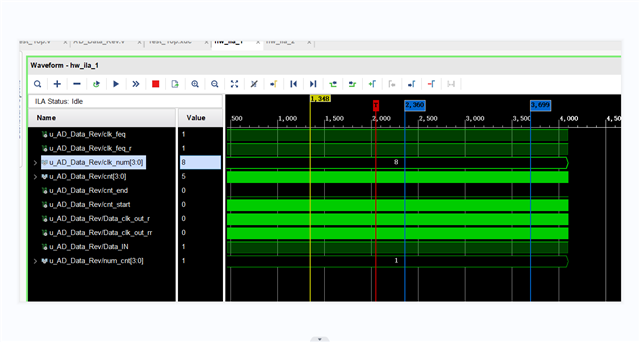

下图是我用FPGA ILA核抓到的信号:显示的就是DCLK是正常方波信号,但是FCLK一直拉高,且ADC的输出引脚DA0也是一直拉高的

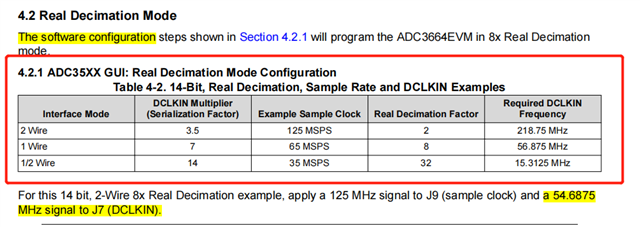

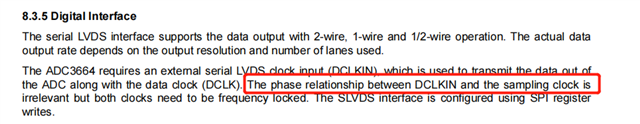

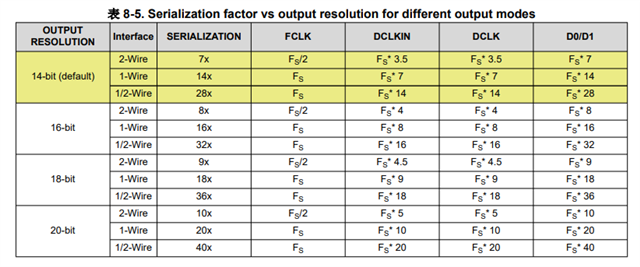

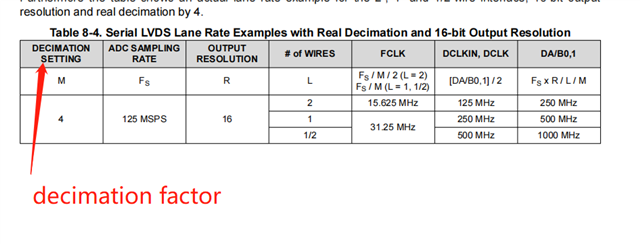

TIP:所有操作基本按照手册指示来进行,且FPGA与ADC3664EVM相连接的引脚已确认过,都是准确的。不明白的地方就是,DCLK和FCLK都是ADC3664返回给FPGA的时钟信号,且二者成7倍关系,即DCLK是FCLK的7倍频(ADC3664配置为14bit的情况时)。