Part Number: ADC3664EVM

Other Parts Discussed in Thread: ADC3664, , CDCE6214

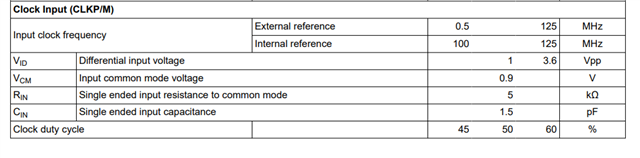

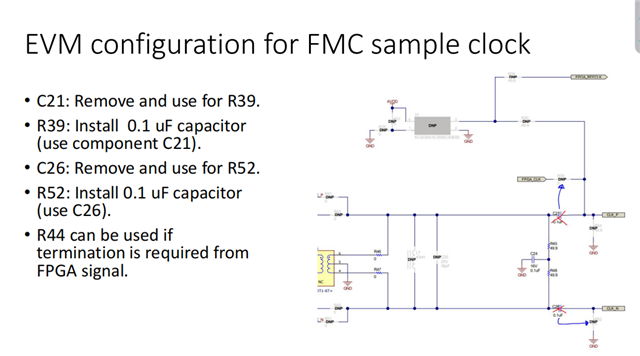

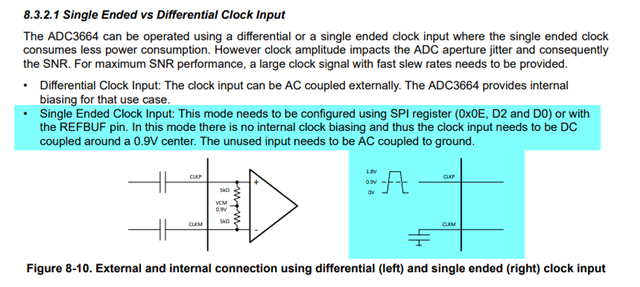

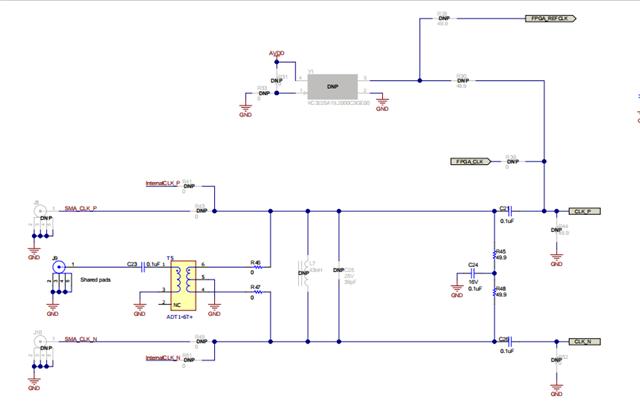

你好,在ADC3664EVM中,采样时钟可以通过J9 balun input进行输入,也可以通过FPGA产生信号时钟,请问如果使用FPGA产生采样时钟给ADC3664的话,下图中的原理图需要进行怎样的修改呢?包括哪些DNP需要重新焊接连接之类的。如果我不需要接受FPGA_REFCLK的话,是不是就只用焊接R39呢?也就是FPGA_CLK。对这个FPGA_CLK有什么幅度需求吗?也就是FPGA这边关于FPGA_CLK这个输出信号引脚有什么配置需求吗,包括电气特性之类的

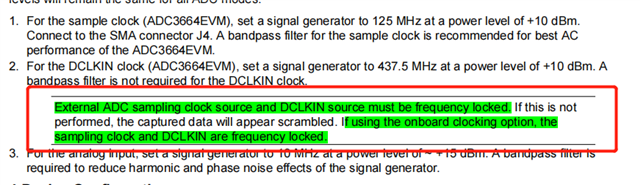

还有一个问题,在ADC3664EVM手册(sbau361.pdf)中讲解到,使用板载时钟就会进行频率锁定。请问这个板载时钟是不是EVM板子上的10M时钟?如果我将ADC配置成14bit 1-wire real decimation,decimation factor=8的话,那么这个板载时钟频率够吗?不清楚怎么配置板载时钟