Part Number: ADS8686S

Hi, Technical Support Team,

I'd like to use ADS8686S for analog acquisition with FPGA,I have some questions about power-supply sequence and RESET pin.

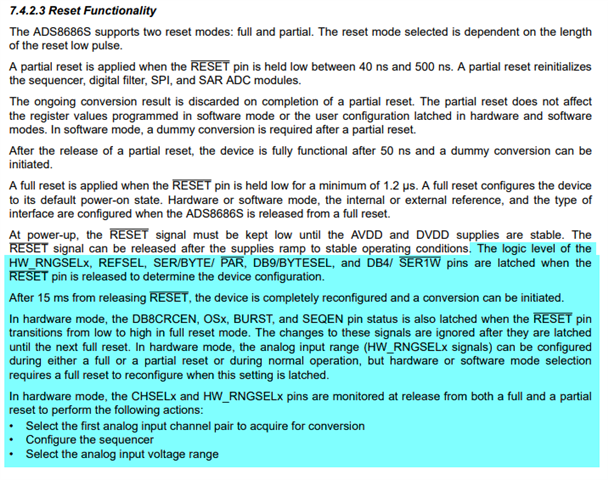

In ADS8686 Datasheet(REV C) Page106, it syas that "Hold RESET low until both supplies are stabilized."

In my current hardware design, ads8686s reset pin is pulled HIGH by pull-up circuit when powered on.

Q1:

Why should hold reset low until both supplies are stabilized?

Q2:

Will it cause any problem if Hold reset HIGH before both supplies are stabilized? Will it stuck?

Q3:

What else can I to avoiding potential issues for my current hardware design? For example, If ads8686 stuck, Powerup reset or Full Reset can work?