Part Number: ADC12DJ3200

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADC12DJ3200

您是否正在使用2个 Xilinx JESD IP、每个 IP 有8个信道?在这种情况下,每个 IP 将生成256位的输出。 斜坡测试模式生成八位位组斜坡(8位值),而不是采样值斜坡(12位值的斜坡)。

建议将 ADC 设置为传输层测试图形模式。者可以让您轻松了解通道数据如何映射到样本,因为帧中的每个样本都有一个恒定的12位值。 此值可在datasheet中的" N 的短传输测试模式= 12模式"表41中找到。

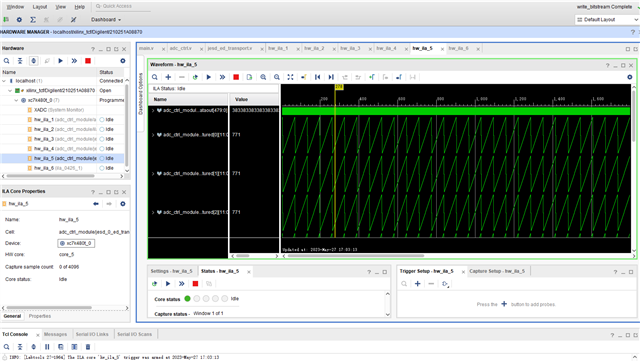

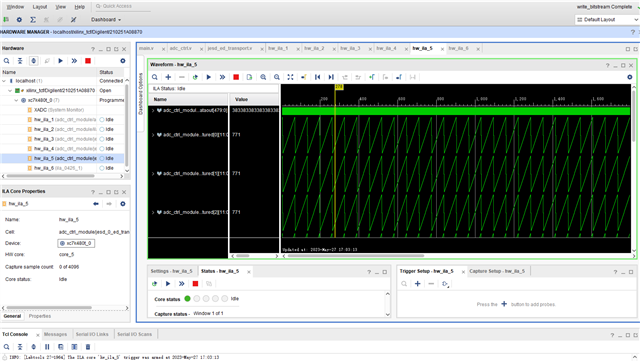

上图是我们使用传输层测试模式生成的图像,目前这个模式下没有问题,但是在采样正弦波时,会出现波动的情况,

目前是使用JMODE1, 在FPGA中使用2个IP核,从FPGA的IP核输出的256位数据到样本的映射分为:

jesd204_0_example_design_1 -> out_data[256:0] ->S0,S2,S4.......S76,S78

jesd204_0_example_design_2 -> out_data_2[256:0] ->S1,S3,S5.....S77,S79

目前看来有点问题,请问哪里需要改正,

您好,非常感谢您的解答,我们重新阅读了器件手册,发现是之前的一个设置没有做好,目前有了稍微正常的采样,但是还是有问题,可否再次询问一下?

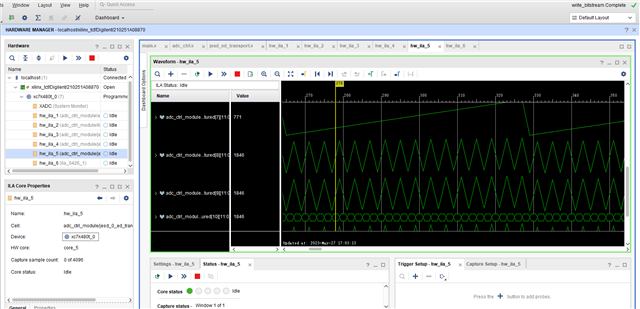

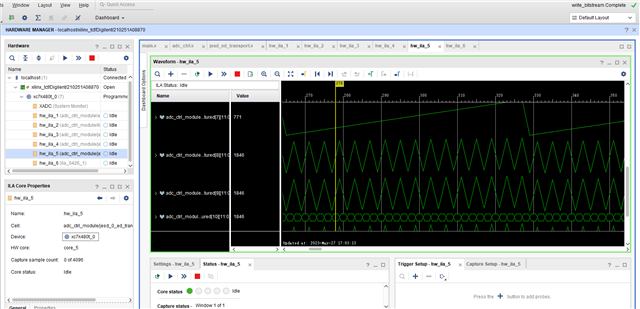

上图是部分采样点,看起来交替起伏,我们估计是采样的校准未做好,目前的校准配置如下:

0:dout<=24'h0000B0; ///***///进行软复位 之后延迟100ms

//时钟50MHz 20ns * 5000 = 100 ms

5001: dout<=24'h020000; ///***///清除 JESD_EN (始终在 CAL_EN 之前)

5002: dout<=24'h006100; ///***///清除 CAL_EN (始终位于 JESD_EN 之后)

5003:dout<=24'h020101;//jmode

5004:dout<=24'h020203;//km

5005:dout<=24'h020301; //非零 即使用 软同步

5006:dout<=24'h020400; //00 01

5007:dout<=24'h020500; //设置JTEST

5008:dout<=24'h0030FF; //设置量程

5009:dout<=24'h0031FF;

5010:dout<=24'h0032FF;

5011:dout<=24'h0033FF;

5012:dout<=24'h002920;

5013:dout<=24'h002960;

5014:dout<=24'h002970; //////将SYSREF_SEL设置为0,使用SYSREF校准

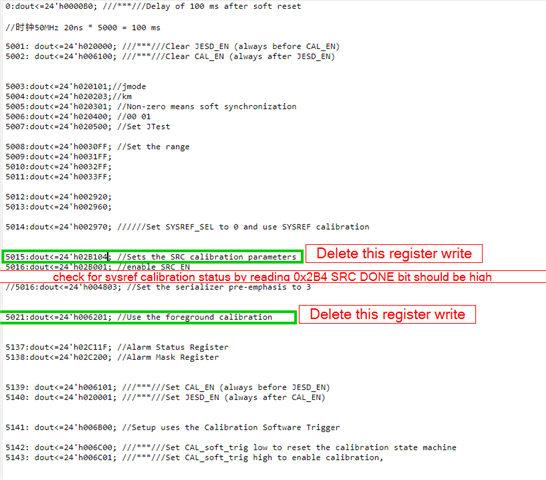

5015:dout<=24'h02B104; //设置SRC校准参数

5016:dout<=24'h02B001; //启用SRC_EN

//5016:dout<=24'h004803; //将串行器预加重设置为3

5021:dout<=24'h006201; //使用foreground校准

5137:dout<=24'h02C11F; //Alarm Status Register

5138:dout<=24'h02C200; //Alarm Mask Register

5139: dout<=24'h006101; ///***///设置 CAL_EN (始终在 JESD_EN 之前)

5140: dout<=24'h020001; ///***///设置 JESD_EN (始终在 CAL_EN 之后)

5141: dout<=24'h006B00; //设置使用Calibration Software Trigger

5142: dout<=24'h006C00; ///***///将 CAL_SOFT_TRIG 设置为低电平以复位校准状态机

5143: dout<=24'h006C01; ///***///将 CAL_SOFT_TRIG 设置为高电平以启用校准 ,

目前0X02C 02D 02E 寄存器的读出分别是 C1 00 86 ,在器件手册中 表 7. Examples of SYSREF_POS Readings and SYSREF_SEL Selections,没有看到SYSREF_POS[23:0] 与 OPTIMAL SYSREF_SEL SETTING 相应的映射,

目前0X2B2 2B3 2B4寄存器的读出分别是 15 4D 02, 表明SRC_DONE 未完成,

目前0X06A寄存器读出是 08,表明FG_DONE 始终未完成,

请问是什么原因?请问有相应的自动foreground校准的配置代码吗?

您好,十分抱歉,我们再来催促下工程师看看,我们把英文论坛的链接给您贴在下面:

请看以下答复:

以下是更新后的寄存器写入:

SCR_DONE 未完成意味着未正确校准 sysref。 请确保 sysref 到达 ADC。