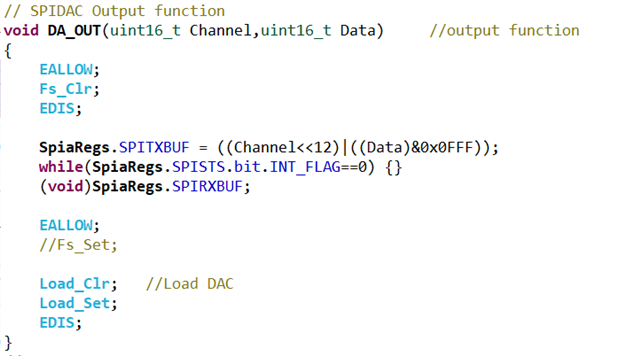

Hi,我在调试TLV5610的时候遇到了一些问题。下图是我最初的SPI程序,依照TI的例程修改而来。DAC芯片输出正常

FS_LOAD,FS_CLR是两个GPIO的宏定义,用于拉高或拉低GPIO。

但我若是将LOAD引脚和片选FS引脚在初始化的时候就拉低,SPIDAC芯片就没有输出了,想问下原因。

另外我还有一个问题,因为在这个程序中我用到了while循环,占用了相当一部分的CPU资源,于是我参考TI的例程将SPI修改为基于DMA,FIFO模式的SPI,在这种条件下我该如何配置FS哈人LOAD管脚呢?