1.现在电路测试测试结果是:

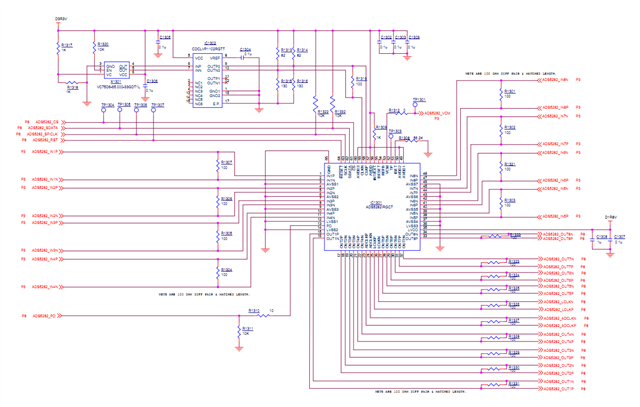

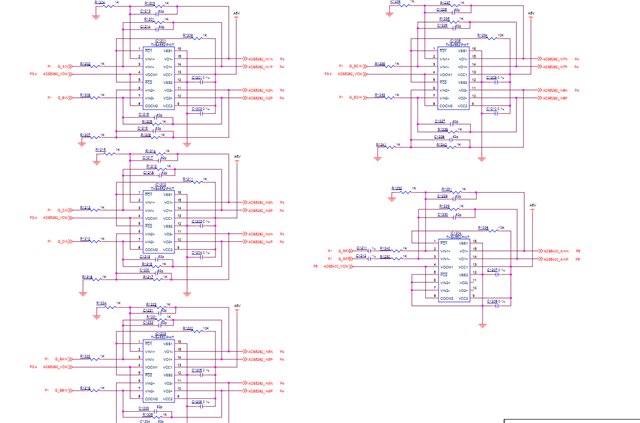

AVDD 3.3V (49, 50, 57, 60) OK

AVSS (3, 6, 9, 37, 40, 43, 46) OK

LVDD 1.8V (35) OK

LVSS (12, 14, 36)

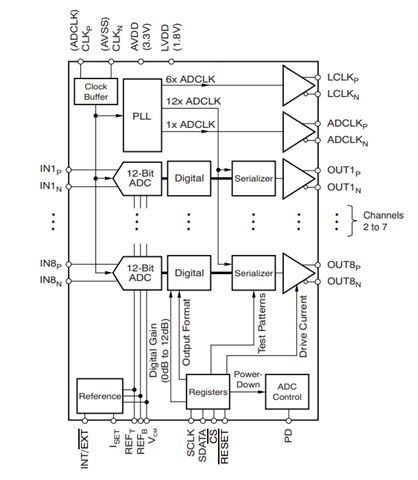

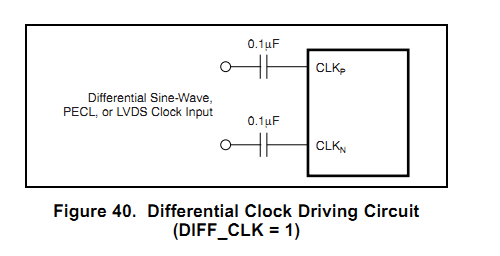

CLKP (58)

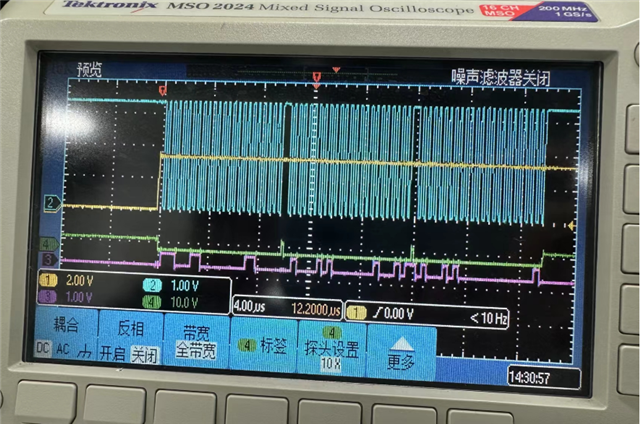

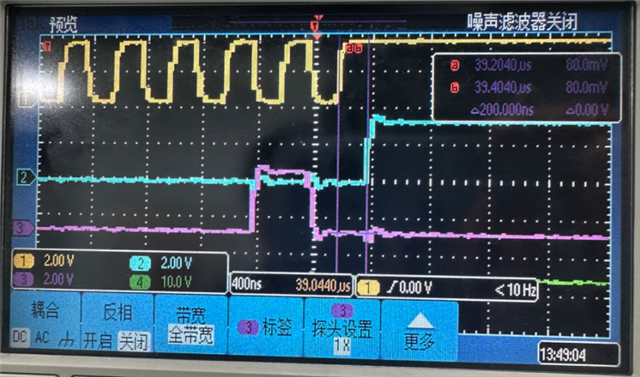

CLKN (59) ADCCLK输入10M晶振输入,1X ADCLK输出正常。6X输出正常。

PD (13) L

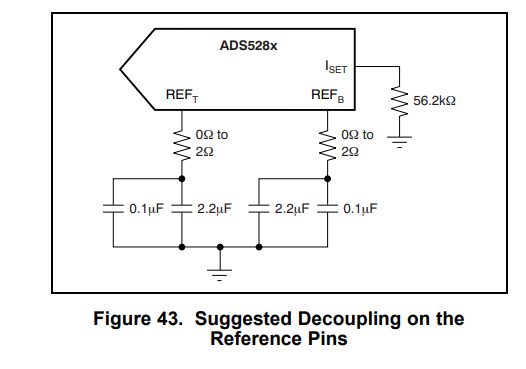

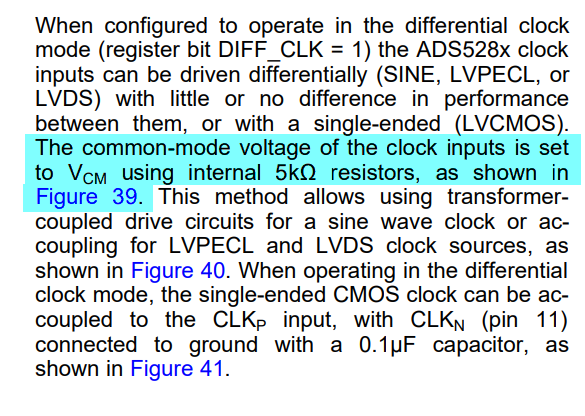

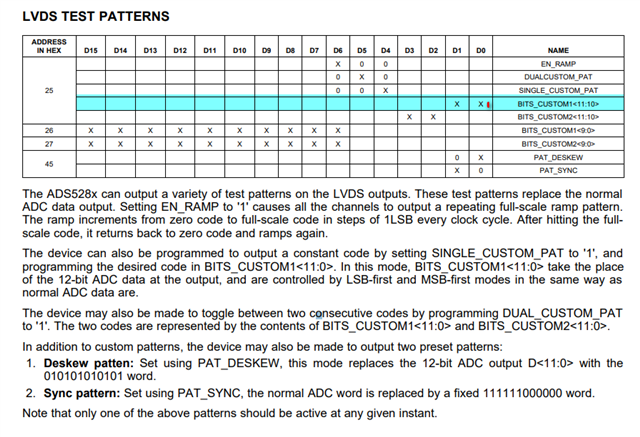

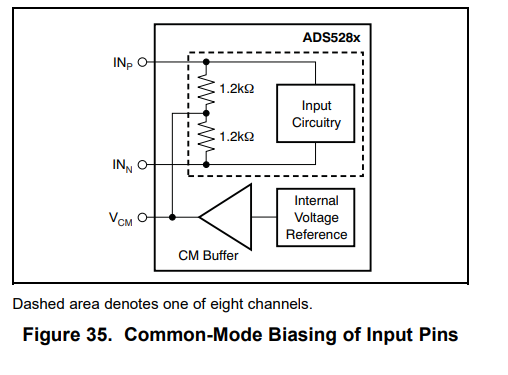

VCM 输出1.5V

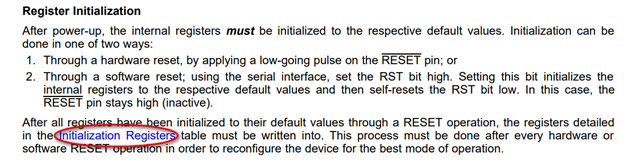

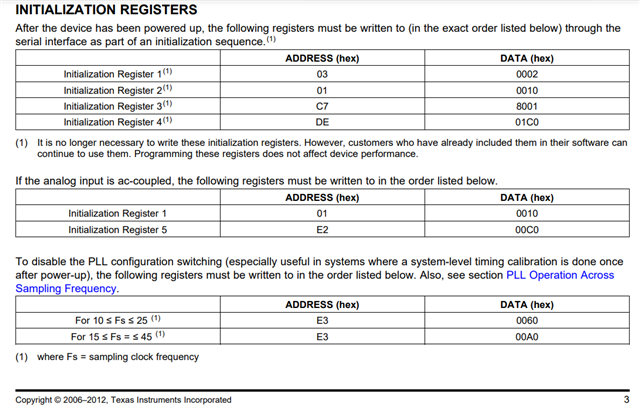

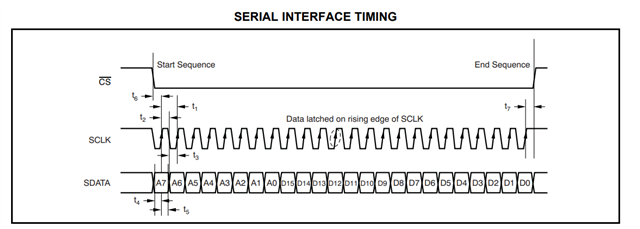

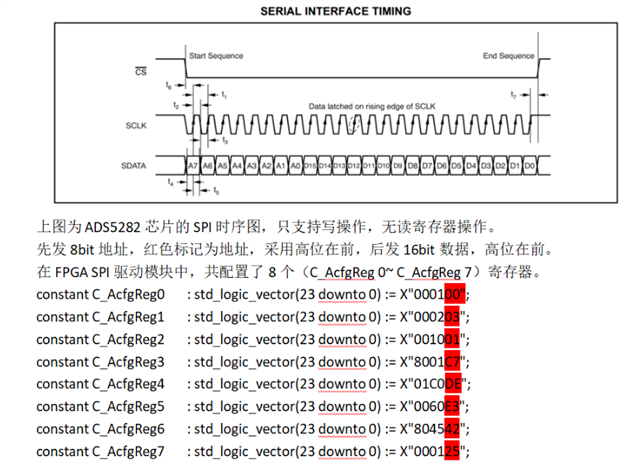

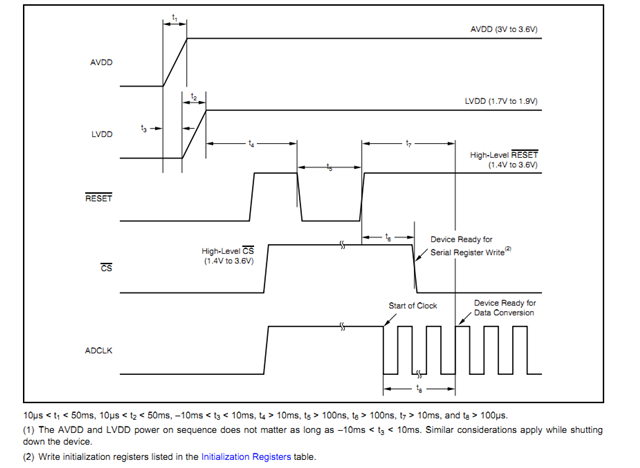

2.RESET管脚连接到FPGA的IO管脚,这个管脚上电默认是高电平。上电后,通过程序控制RESET拉低后,再拉高。

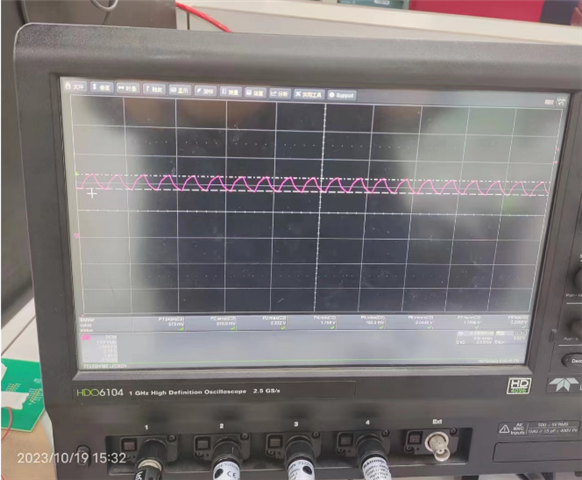

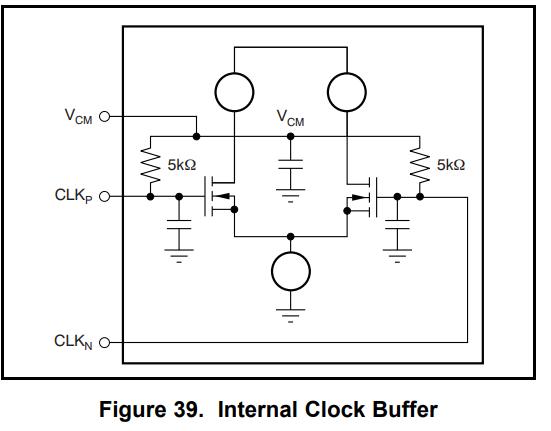

现在寄存器设置CMD45 在PAT_SYNC模式下,示波器测试任何ADC通道都没有信号输出。

我想咨询下:

1.如果VCM和PLL单元的信号输出正常。能表明IC的1.8V模块所以功能是正常?

2.在PAT_SYNC模式下,示波器测试任何ADC通道都没有信号输出是什么原因?