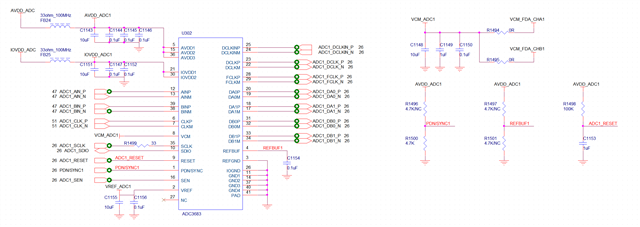

Part Number: ADC3683

工程师您好!

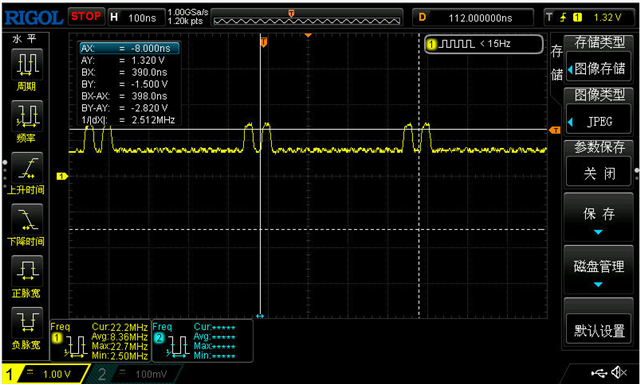

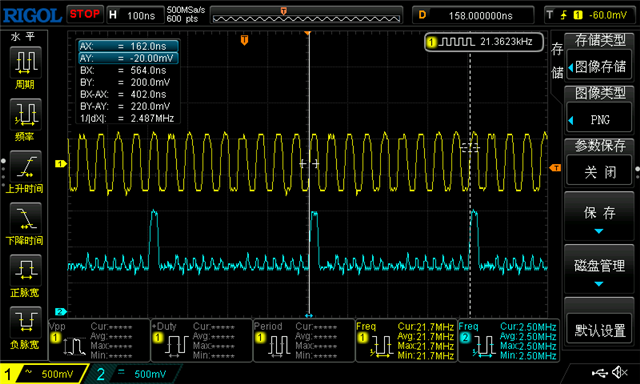

我们现在使用ADC3683,发现FCLK的输出占空比不是50/50:(黄色为DCLK,蓝色为FCLK)

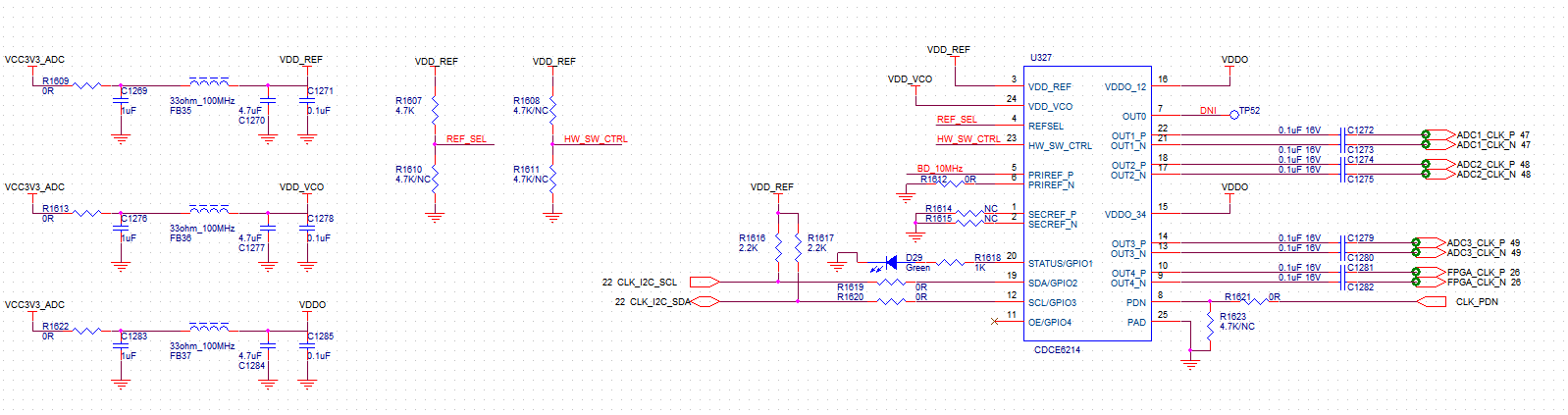

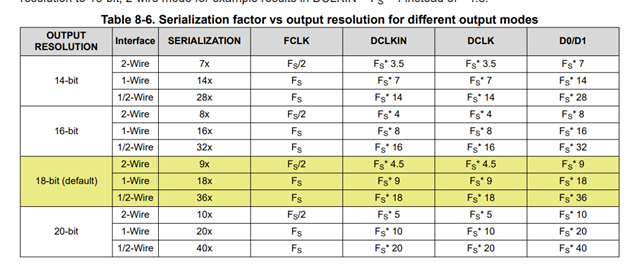

我们使用如下模式:

Real Decimation, 1-wire,Decimation by 4

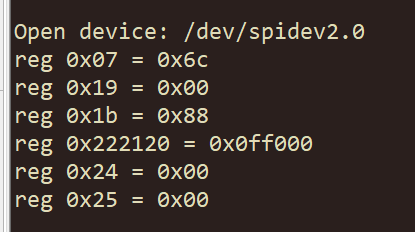

寄存器配置如下:

write_reg(fd, 0x07, 0x6c);

// load e-fuse

write_reg(fd, 0x13, 0x01);

usleep(2000);

write_reg(fd, 0x13, 0x00);

usleep(2000);

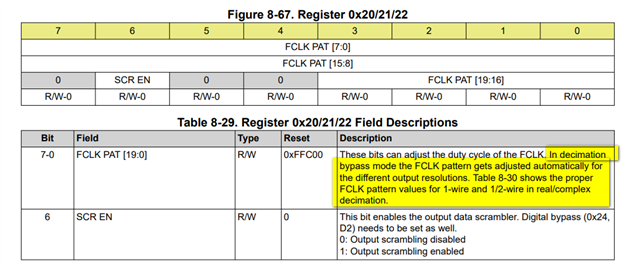

// configure FCLK

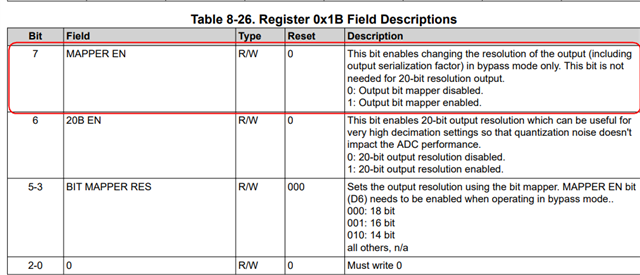

write_reg(fd, 0x19, 0x00);

write_reg(fd, 0x1B, 0x00);

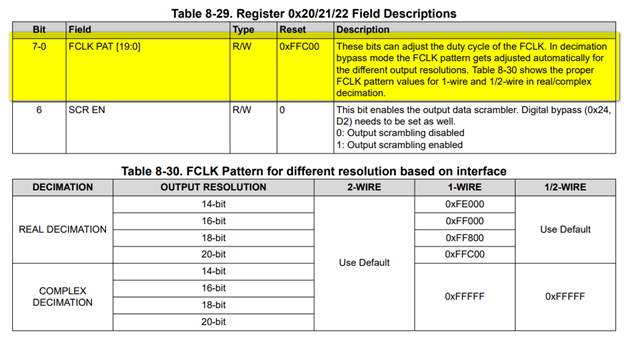

// REAL DECIMATION, 18-bit, 1-WIRE, 0xFF800

write_reg(fd, 0x20, 0x00);

write_reg(fd, 0x21, 0xF8);

write_reg(fd, 0x22, 0x0F);

// Enable the decimation filter

write_reg(fd, 0x24, 0x06);

// Configure the decimation filter

// Decimation by 4, Real decimation

// 0 010 1 00 0

write_reg(fd, 0x25, 0x28);

// real decimation

write_reg(fd, 0x27, 0x00);

write_reg(fd, 0x2E, 0x00);

// no gain added

write_reg(fd, 0x26, 0x22);

write_reg(fd, 0x26, 0x00);

请问是不是哪里配置有误?

感谢!