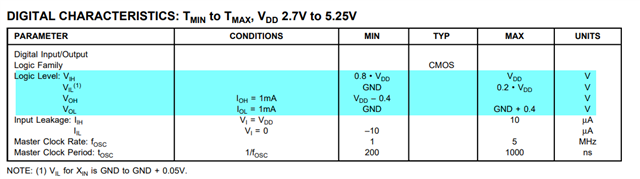

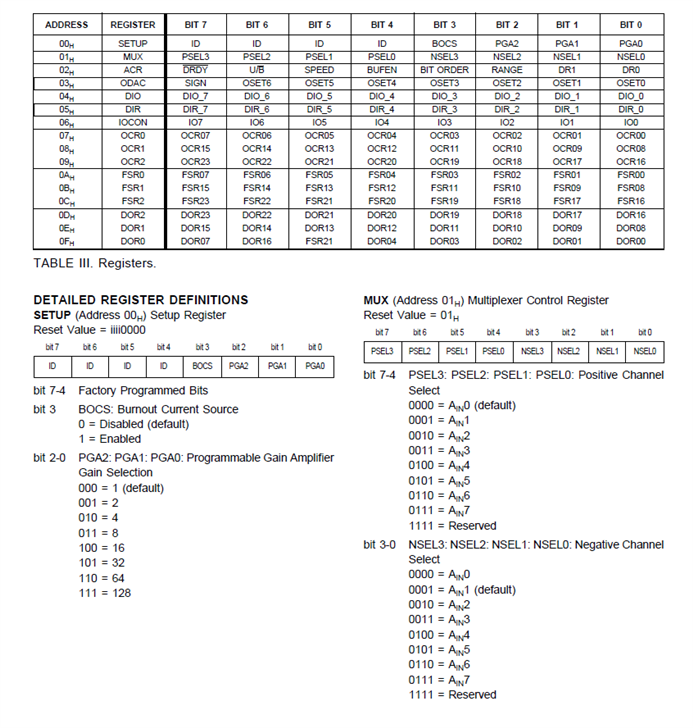

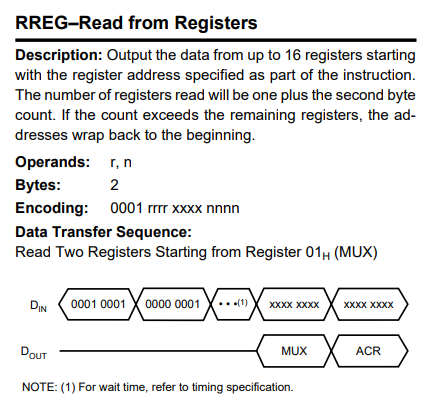

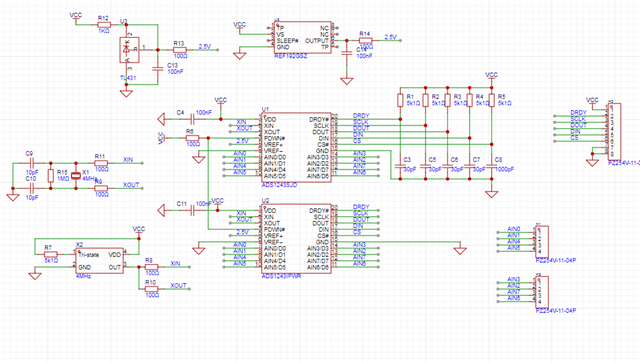

3.3V的电源,MCU在读取ADS1243数据时,SPI的SCLK管脚设置为外部上拉时无法正确读取到寄存器的值,外部上拉电阻为5.1K,SPI的SCLK管脚配置为推挽时读取就可以。

本来是用5V的单片机读取发现有问题,就改成3.3V的单片机读取试下,就发现了该问题,为什么会出现这种现象。

所有上拉电阻选型为5.1K

电路看着应该没啥问题,单片机的SCLK、MOSI、CS都配置成开漏外部上拉,MISO配置成外部上拉输入,读取寄存器错误。

单片机的MOSI、CS配置成开漏外部上拉,MISO配置成外部上拉输入,SCLK的配置成推挽,读取寄存器就正确。

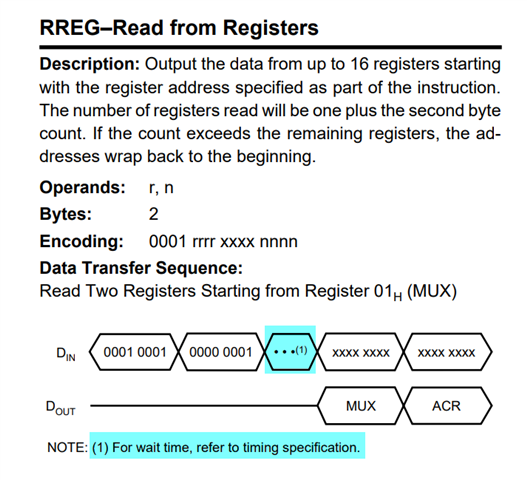

写寄存器都没有问题和SCLK上拉推挽无关,读寄存器存在问题,配置完ADS1243后,开始读取寄存器值。

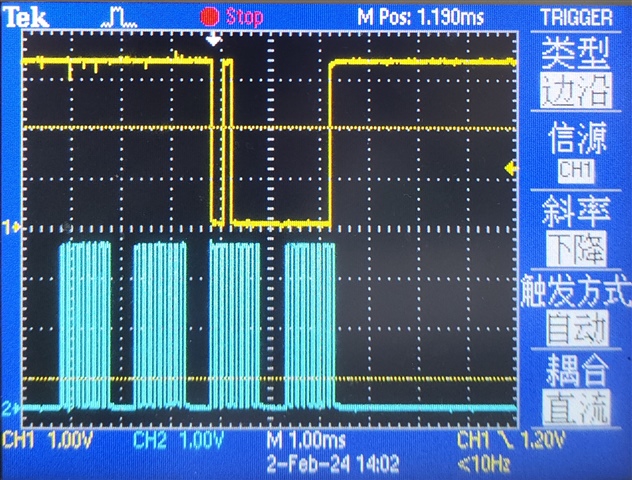

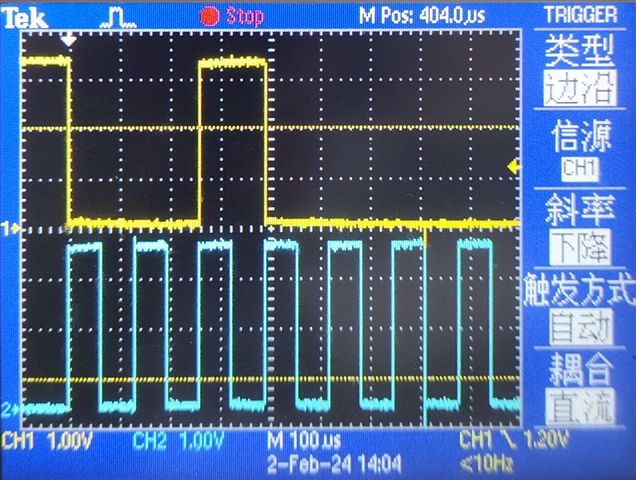

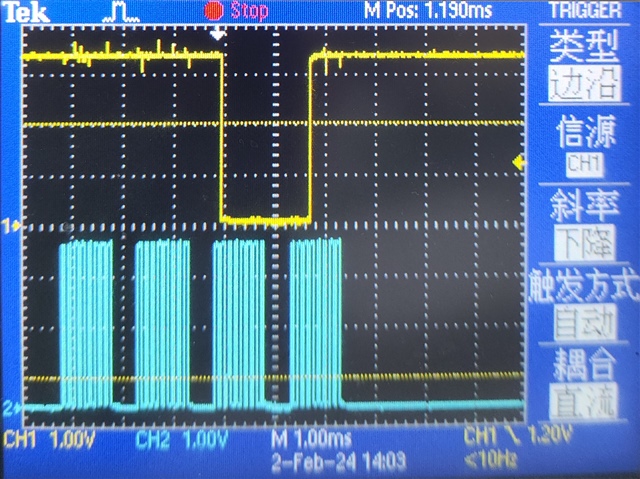

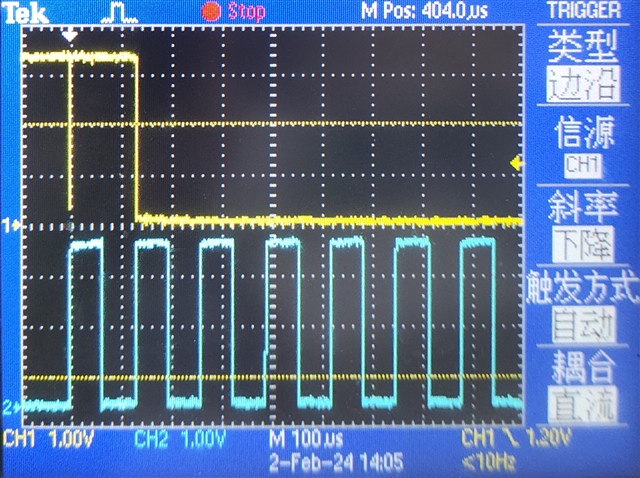

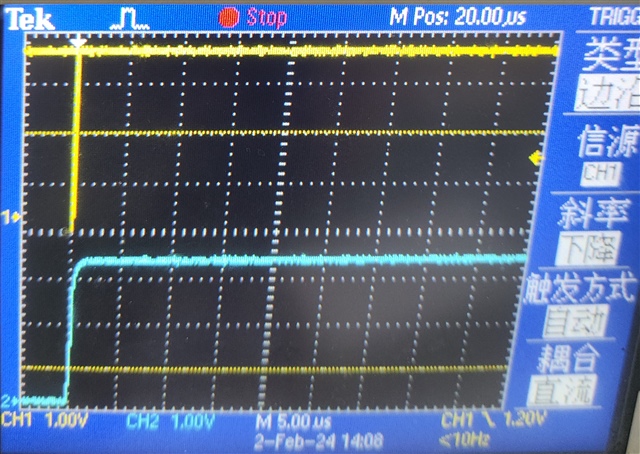

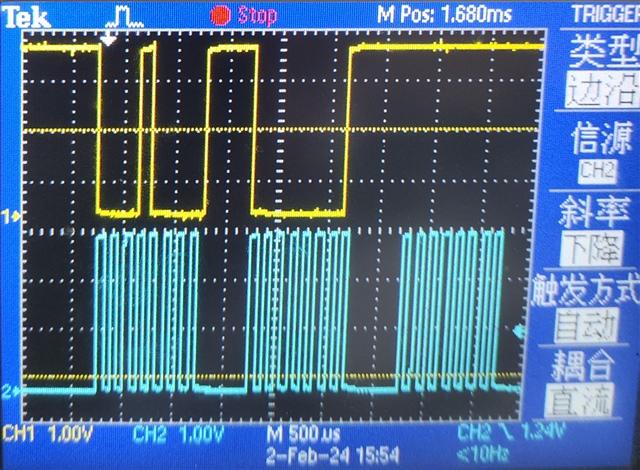

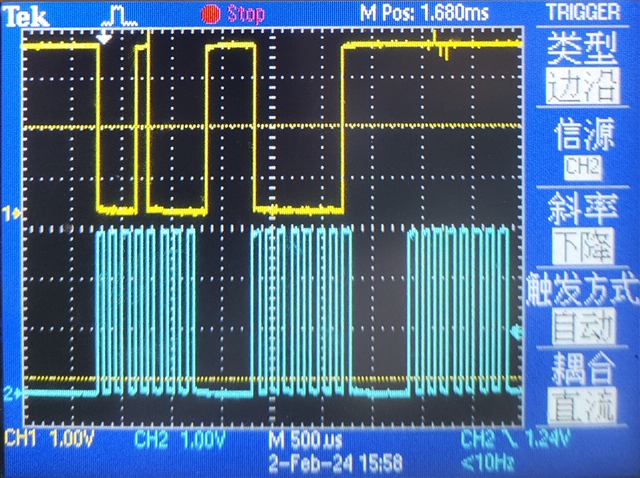

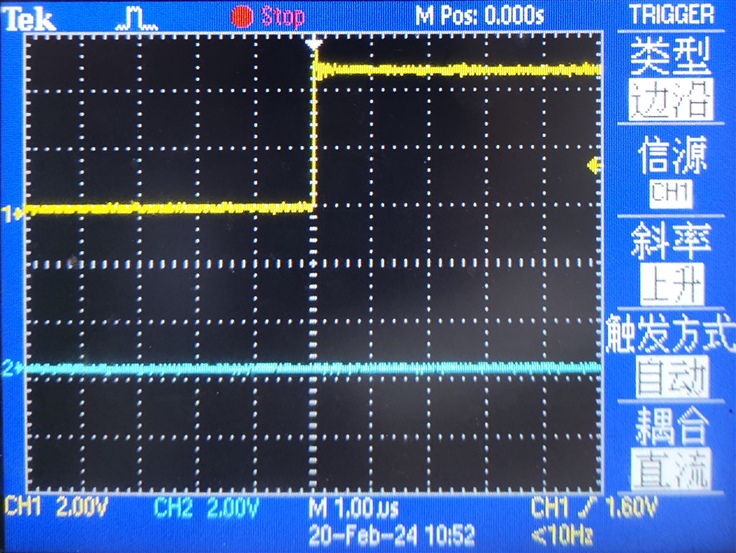

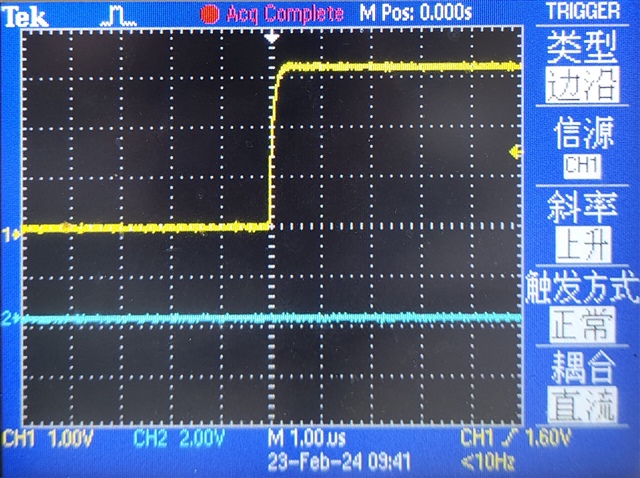

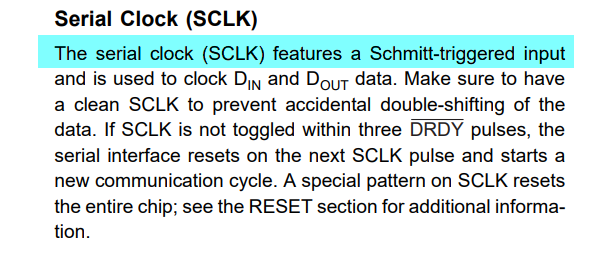

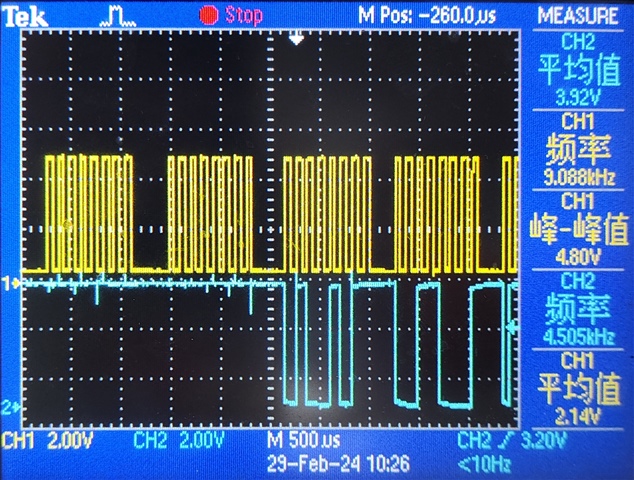

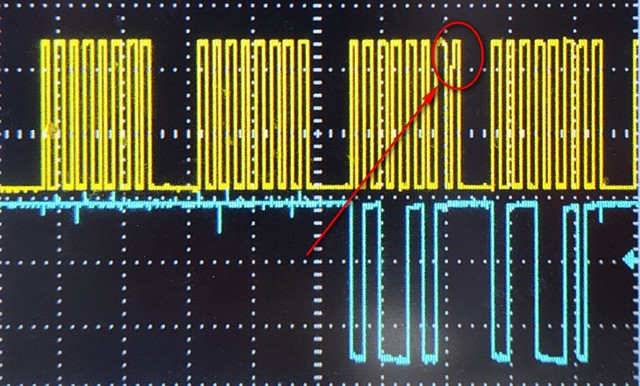

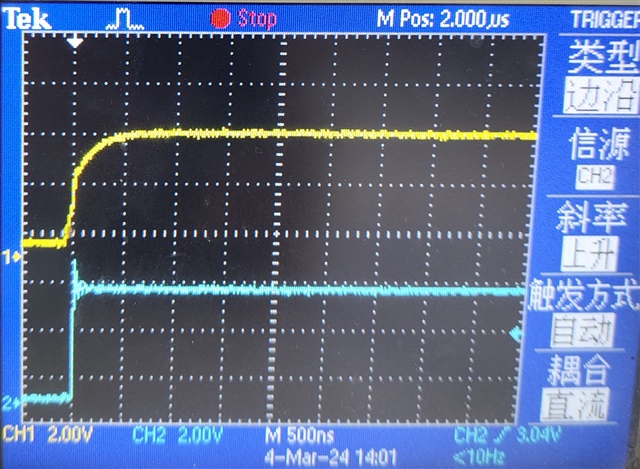

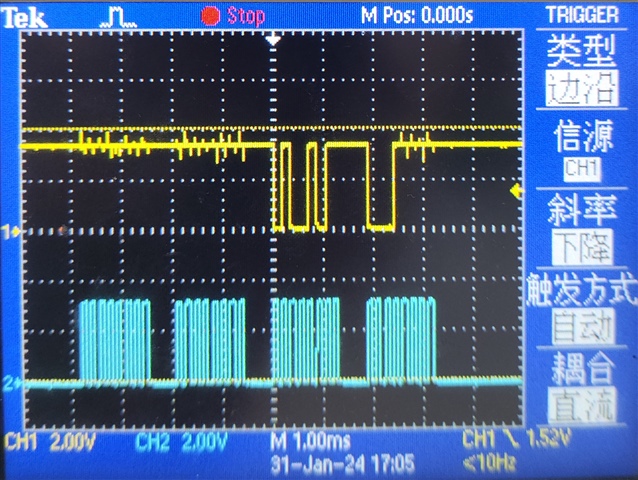

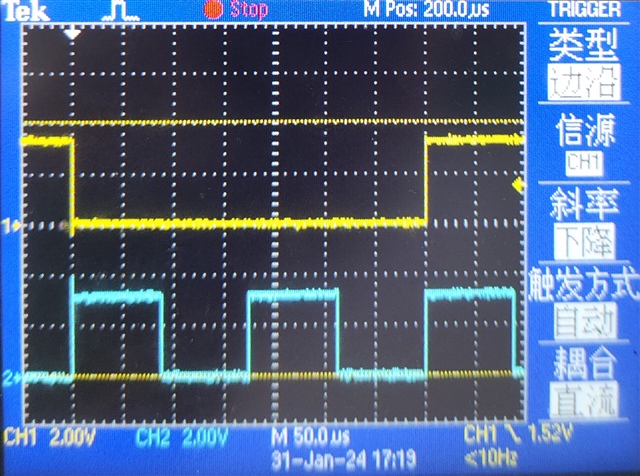

下图为读取错误示波器图片

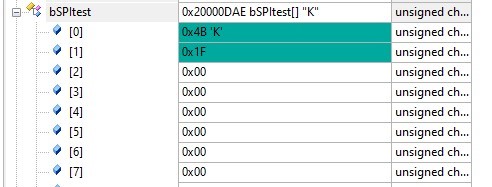

SCLK开漏外部上拉ADS1243读取错误0x4B,0x1F

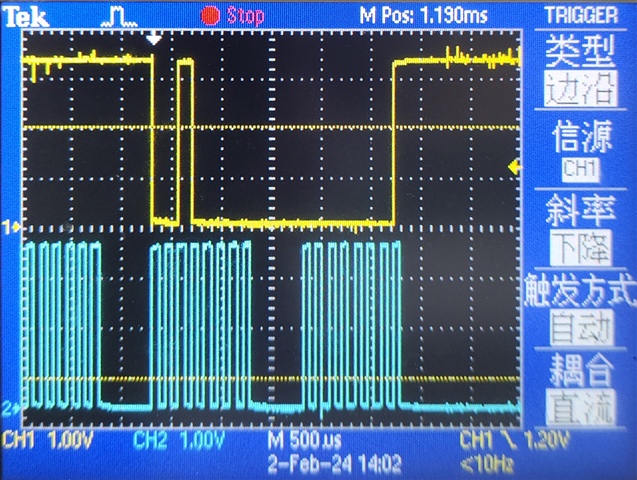

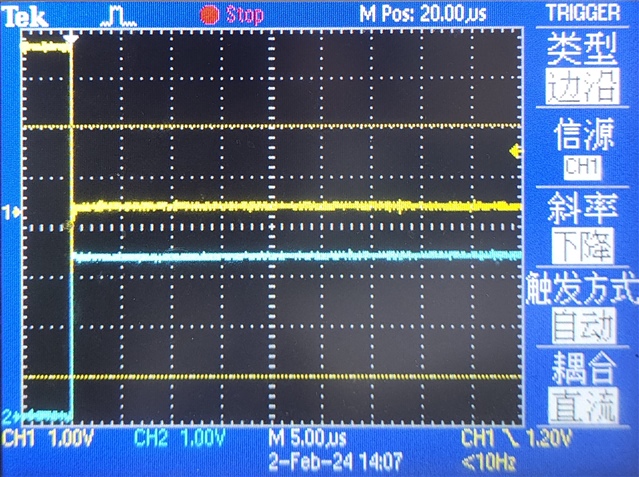

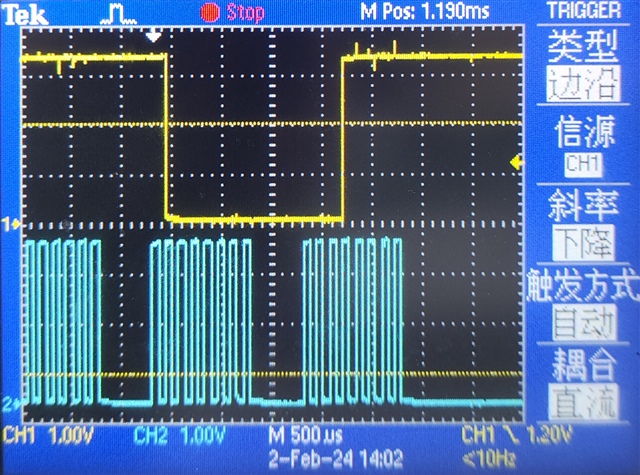

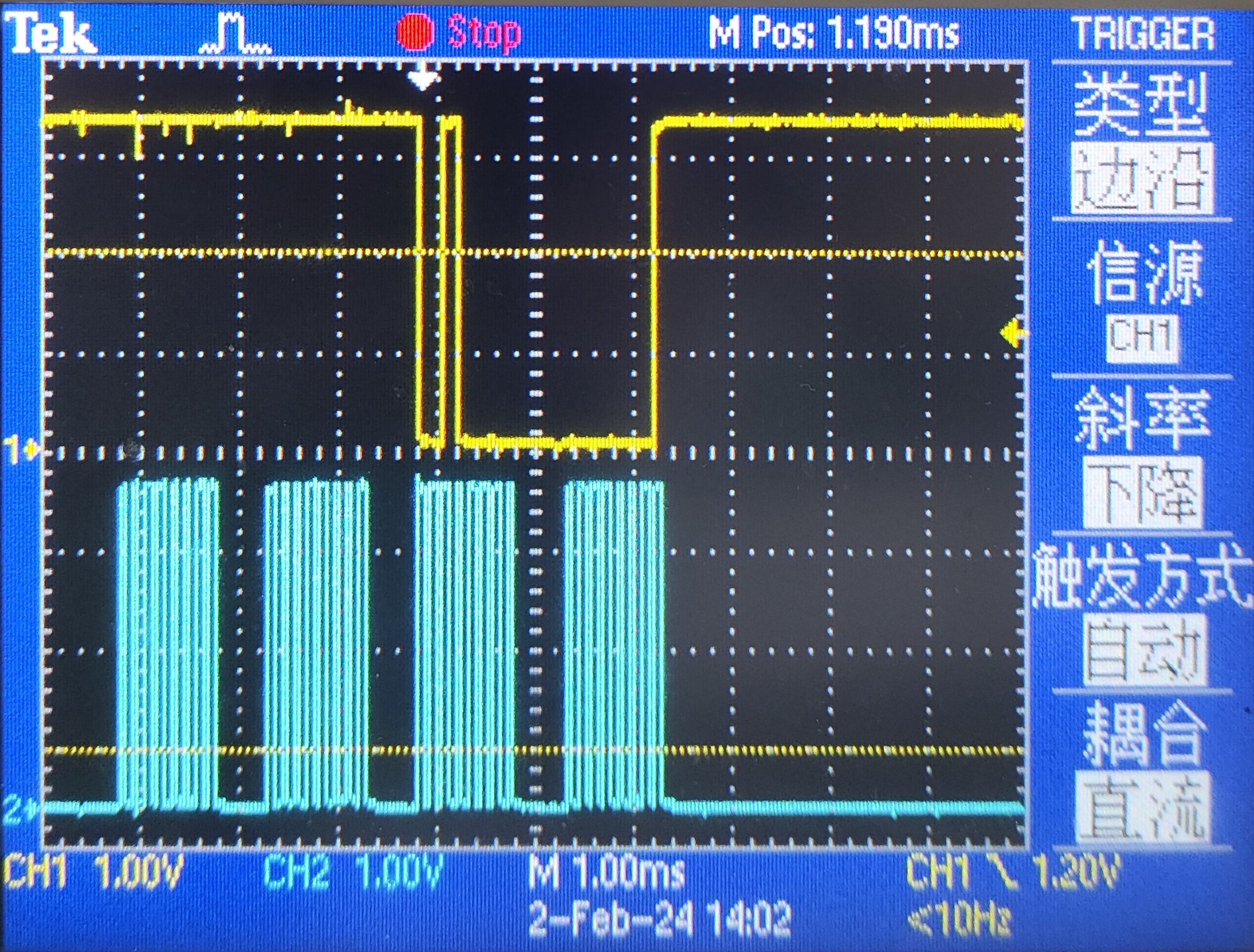

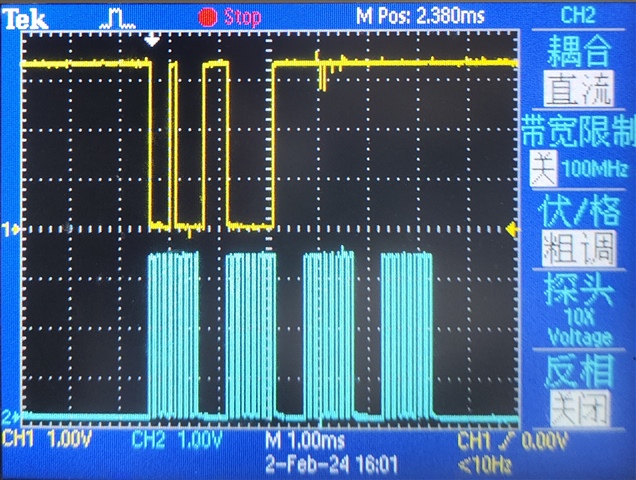

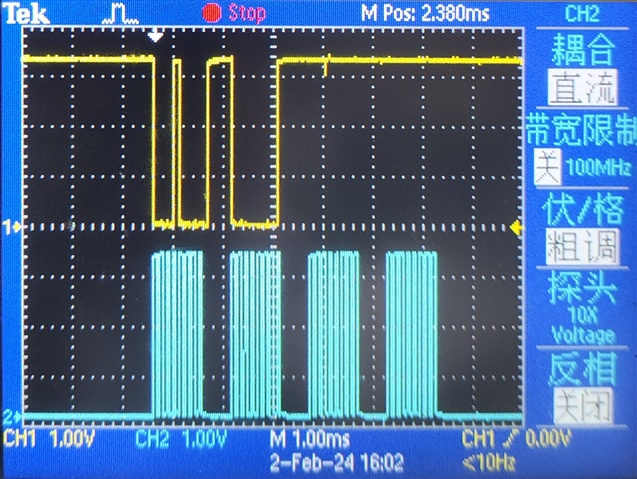

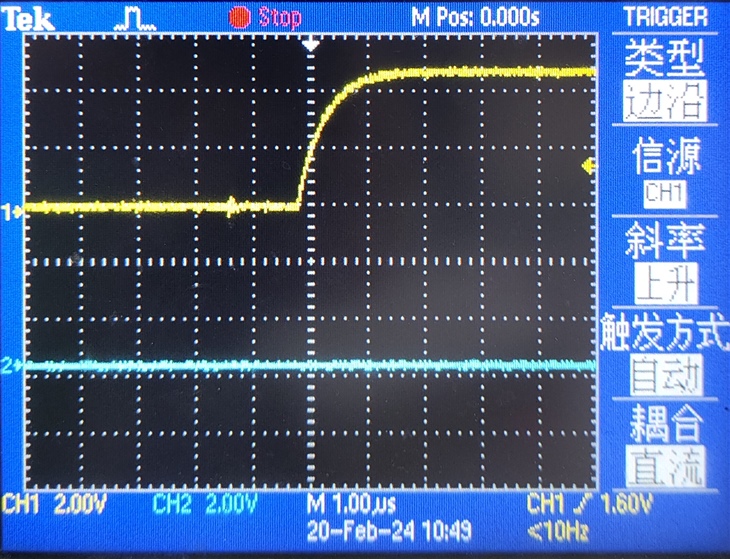

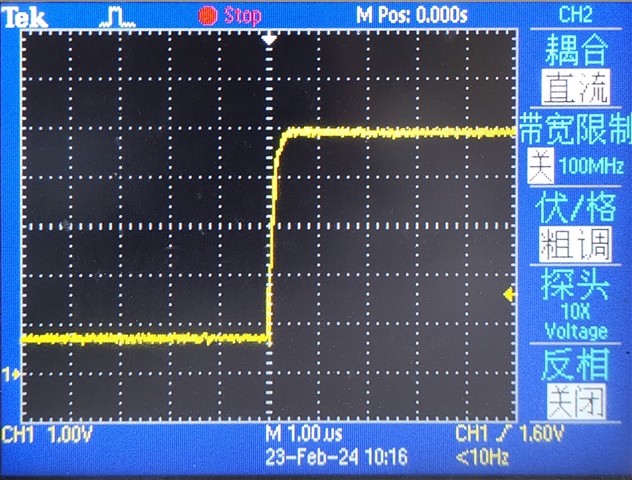

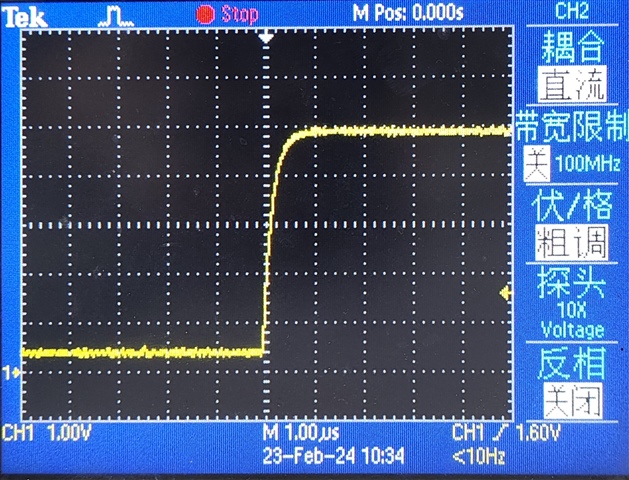

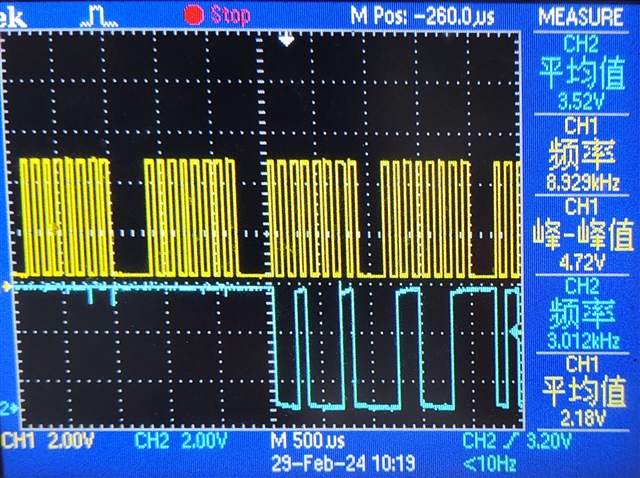

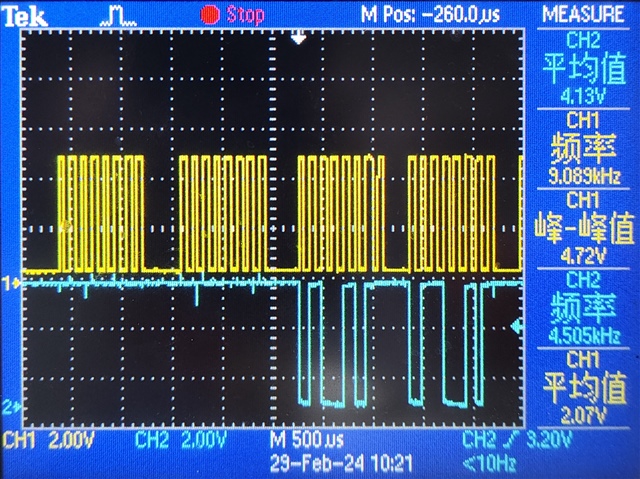

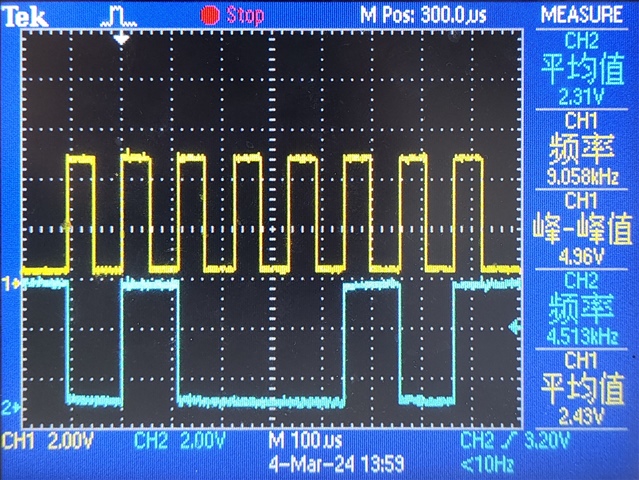

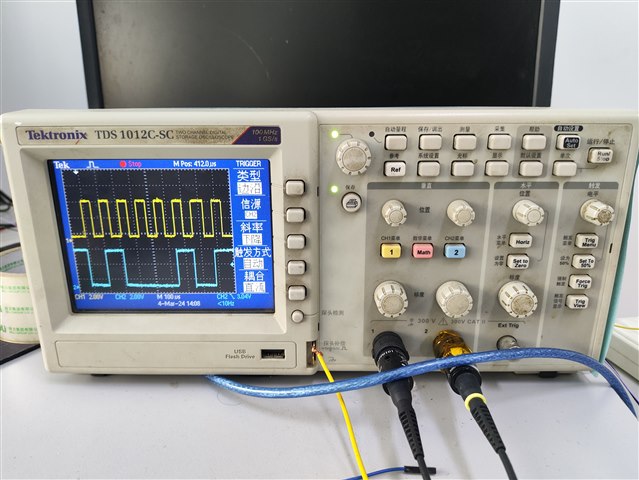

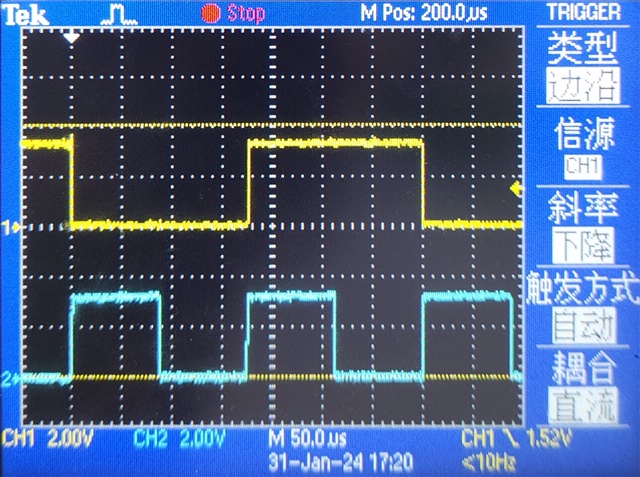

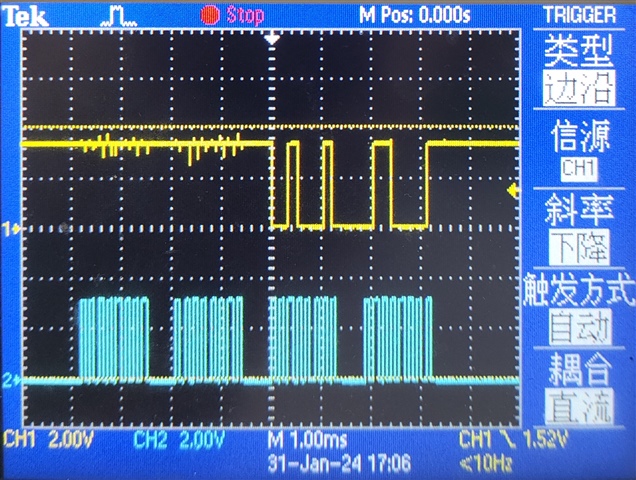

下图为读取正确示波器图片

SCLK推挽ADS1243读取正确0x22,0x61

ADS1243写寄存器,SCLK推挽和开漏外部上拉都正常,通过反复配成推挽或开漏测试无影响,只要保证读的时候SCLK配置成推挽,读的数据都是正确的,说明写寄存器和SCLK推挽或开漏外部上拉无关。

由于使用条件有限必须搞清楚为啥SCLK外部上拉存在问题是使用方法不当还是别的什么问题,请教老师前辈们给指导下