Other Parts Discussed in Thread: LMX2531, ADC12D1800, LMX2581, JITTER-SNR-CALC

目前我采用的芯片为ADC12D18000,工作方式主要有三种:

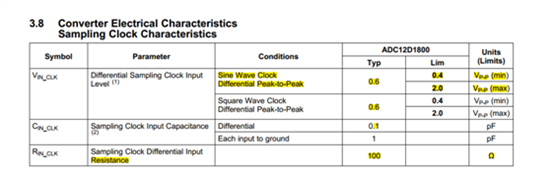

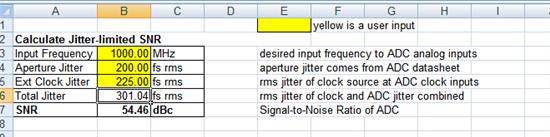

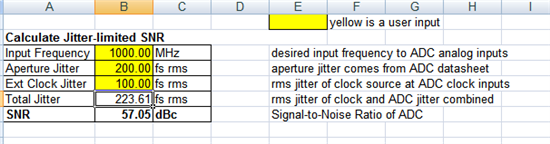

第一种采用两个芯片构成4通道,也就是2个ADC正常工作,采样率为500MSPS,工作时钟500MHZ,工作状态为NON-DES Mode ;

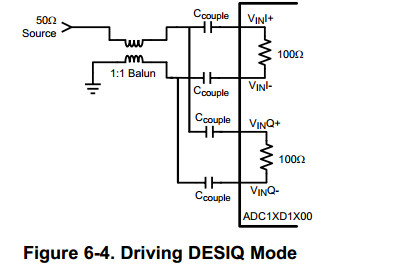

第二种采用2通道,一片ADC正常工作,另外一个ADC处于POWER DOWN状态,数据采样率为2GSPS,利用内部的DES模式,工作时钟为1GHZ;

第三种只用一个通道,一片ADC处于POWER Down,另一外一片ADC中的Q通道处于POWER DOWN,数据采样率为1GSPS,工作时钟为1GHZ;工作状态为NON-DES Mode ;

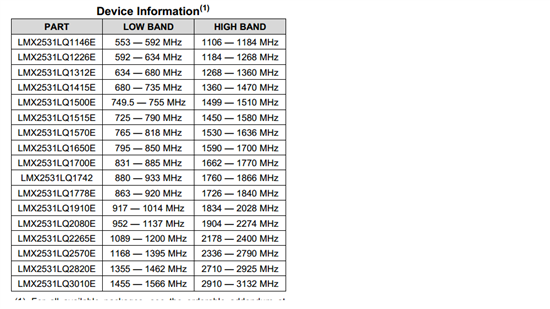

三种功能都是在同一板块上实现,通道模式的由FPGA控制,FPGA采用的型号为XC7VX485T。设计中推荐的时钟芯片为LMX2531显然不符合我的要求

问题:

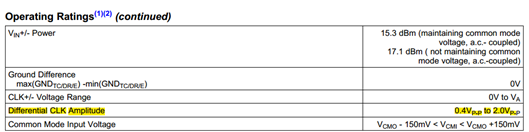

1 时钟芯片的输入是LVCMOS,电平标准是3.3V,输入频率要包括10M和100M即可(最好额外还支持晶振输入,晶振频率无要求);类似IDT的8T49N287,资料见附件;

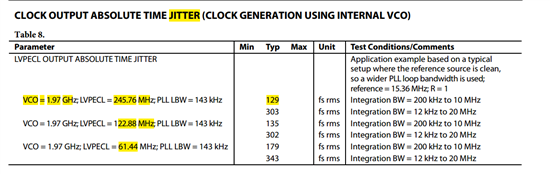

2 考虑系统时钟同步问题,所以我还需要产生200M或者250M,需要4路,所以相当于整个时钟芯片至少需要6路,其中2路需要能够达到500M和1G用于ADC工作时钟;

3 关于电平标准,由于ADC的工作电源为1.9V,FPGA的工作电压为1.8V,数据时钟和数据信号可以直接输送给FPGA处理吗,需要电平转换不。 FPGA资料见路径:xgoogle.xilinx.com/search

文件名:DS183

4 ADC的电源依据手册说要线性电源,可否采用开关电源,如果有好的建议,请推荐。

5 依据现有资料表明,ADC的所有地都应该统一为一种地,也就是说只分区不分地,请问有相关的理论文档不。

谢谢!