Part Number: ADS54J60

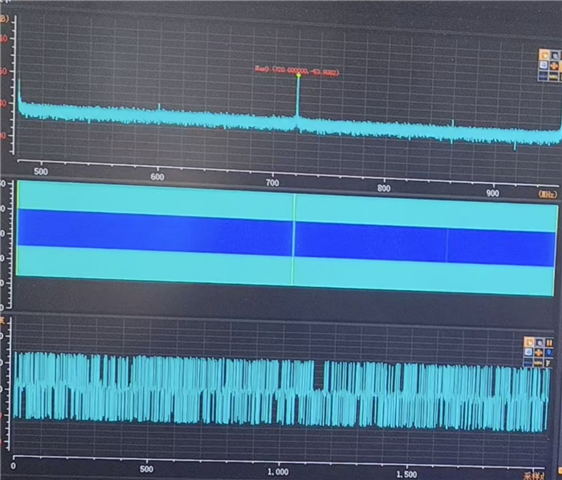

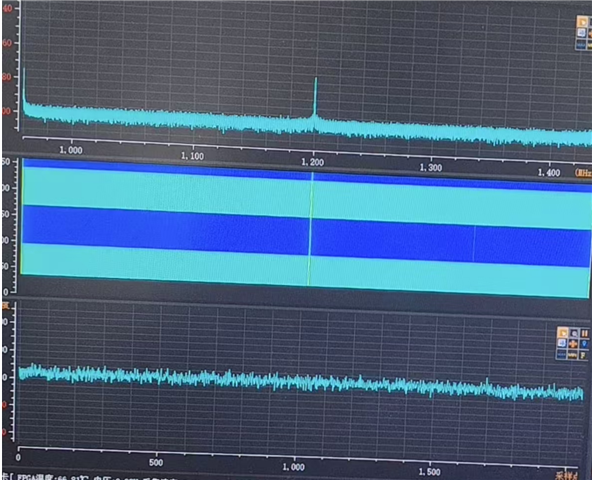

你好,我做的子卡是采用两片ADS54J60,总共四个通道输入,测试的时候发现其中一块芯片的底噪上面叠加了一个比较大的信号,另外一块芯片是正常的,这种情况一般是什么原因导致的呢?下图是第一张是底噪被抬高的图片,第二张是正常的底噪

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好

一般通过这几点去排查。

电源是否纹波和噪声低的,同时数模电源分开

基准源是否有偏差,同时进行滤波

时钟源低噪声低抖动

信号源是否干净, 防混叠,滤波高频噪声

如果您使用两颗,也可以对比一下这两颗芯片周围的电路是否不一样,其中一颗芯片附近是否有干扰;单独测试其中一颗,是否还会有较大的噪声;将两颗芯片互换位置,检查是否是芯片本身的问题。

您用公司邮箱注册TI账号,然后在英文论坛发(e2e.ti.com/)帖咨询一下我们产品线,最好是把原理图,PCB和相关代码都附上,让他们再为您排查一下。