Part Number: ADC12DJ5200RF

Other Parts Discussed in Thread: ADC12DJ3200

你好

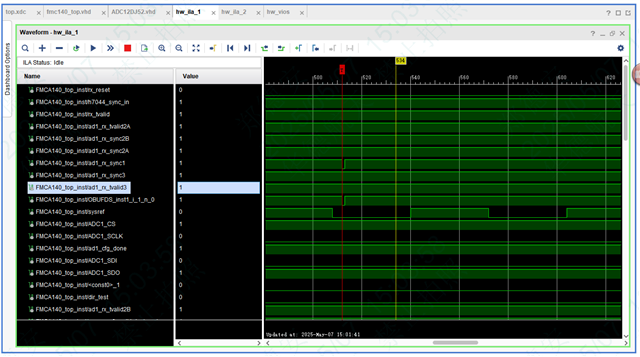

我在使用ADC12DJ5200芯片时,遇到SYNC有概率性拉低问题,请协助解决一下该问题,谢谢

我使用的配置是mode19;采样率9.6G,核时钟300M,线速度12G,sysref 18.75M;

配置如下;请查看配置是否有异常,谢谢

when x"00" =>

ad_config_reg <= x"0000" & x"B0"; --复位,自动置位;需要等待

NEED_DELAY <= x"0000000000080000";

BIR <= '0';

when x"01" =>

ad_config_reg <= x"0000" & x"30"; --

NEED_DELAY <= x"0000000000080000";

BIR <= '0';

when x"02" =>

ad_config_reg <= x"0002" & x"00"; -- PD

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"03" =>

-- ad_config_reg <= x"8003" & x"03"; --CHIP_TYPE

-- NEED_DELAY <= x"00000000";

-- BIR <= '0';

ad_config_reg <= x"0200" & x"00"; --Always set CAL_EN before setting JESD_EN ;Always clear JESD_EN before clearing CAL_EN--------------------------

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"04" =>

ad_config_reg <= x"0004" & x"21"; -- CHIP_ID ADC12DJ3200

NEED_DELAY <= x"0000000000000000";

BIR <= '1';

when x"05" =>

ad_config_reg <= x"0029" & x"60"; --Enable the SYSREF---------------------------------------------------

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"06" =>

ad_config_reg <= x"002A" & x"00"; --Inverts the SYSREF

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

-- when x"07" =>

-- ad_config_reg <= x"802C" & x"00"; --SYSREF_POS R

-- NEED_DELAY <= x"00000000";

-- BIR <= '0';

-- when x"08" =>

-- ad_config_reg <= x"802D" & x"00"; --SYSREF_POS R

-- NEED_DELAY <= x"00000000";

-- BIR <= '0';

-- when x"09" =>

-- ad_config_reg <= x"802E" & x"00"; --SYSREF_POS R

-- NEED_DELAY <= x"00000000";

-- BIR <= '0';

when x"0A" =>

ad_config_reg <= x"0030" & x"FF"; --Full Scale RangeA 1VPP

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"0B" =>

ad_config_reg <= x"0031" & x"FF"; --Full Scale RangeA 1VPP

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"0C" =>

ad_config_reg <= x"0032" & x"FF"; --Full Scale RangeB 1VPP

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"0D" =>

ad_config_reg <= x"0033" & x"FF"; --Full Scale RangeB 1VPP

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"0E" =>

ad_config_reg <= x"0038" & x"00"; -- BG_BYPASS

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"0F" =>

ad_config_reg <= x"003B" & x"01"; --differential TMSTP+/- input

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"10" =>

ad_config_reg <= x"0048" & x"00"; -- pre-emphasis

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"11" =>

ad_config_reg <= x"0060" & x"01"; -- no swap;which input is sampled in single channel mode.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"12" =>----------------------------------------------------------------配置完开启校准;确保JESD关闭;

ad_config_reg <= x"0061" & x"00"; -- Calibration Enable. Always set CAL_EN before setting JESD_EN. Always clear JESD_EN before clearing CAL_EN.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"13" =>

ad_config_reg <= x"0062" & x"01"; -- background calibration

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

-- when x"14" =>

-- ad_config_reg <= x"806A" & x"01"; -- foreground calibration has completed

-- NEED_DELAY <= x"00000000";

-- BIR <= '0';

when x"15" =>

ad_config_reg <= x"006B" & x"00"; -- Use the CAL_SOFT_TRIG register for the calibration trigger

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"16" =>

ad_config_reg <= x"006C" & x"00"; -- CAL_SOFT_TRIG

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"17" =>

ad_config_reg <= x"006E" & x"88"; -- how long an ADC sleeps before waking up for calibration

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"18" =>

ad_config_reg <= x"0070" & x"00"; --CAL_DATA_EN

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"19" =>

ad_config_reg <= x"0071" & x"00"; -- CAL_DATA

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"1A" =>

ad_config_reg <= x"007A" & x"00"; -- A Gain Trim

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"1B" =>

ad_config_reg <= x"007B" & x"00"; -- B Gain Trim

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"1C" =>

ad_config_reg <= x"007C" & x"00"; -- Band-Gap Reference Trim

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"1D" =>

ad_config_reg <= x"007E" & x"00"; --VINA Input Resistor Trim

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"1E" =>

ad_config_reg <= x"007F" & x"00"; -- B Input Resistor Trim

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"1F" =>

ad_config_reg <= x"0080" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"20" =>

ad_config_reg <= x"0081" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"21" =>

ad_config_reg <= x"0082" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"22" =>

ad_config_reg <= x"0083" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"23" =>

ad_config_reg <= x"0084" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"24" =>

ad_config_reg <= x"0085" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"25" =>

ad_config_reg <= x"0086" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"26" =>

ad_config_reg <= x"0087" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"27" =>

ad_config_reg <= x"0088" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"28" =>

ad_config_reg <= x"0089" & x"00"; -- adjust the sampling instant of each ADC core.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"35" =>

ad_config_reg <= x"0097" & x"00"; -- thus filtering all DC content in the signal.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"36" =>

ad_config_reg <= x"0098" & x"33"; -- adjusts the IIR filter bandwidth for the offset filtering feature

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"37" =>

ad_config_reg <= x"0102" & x"00"; -- Time adjustment for bank 0

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"38" =>

ad_config_reg <= x"0103" & x"00"; -- Time adjustment for bank 0

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"39" =>

ad_config_reg <= x"0112" & x"00"; -- Time adjustment for bank 1

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"3A" =>

ad_config_reg <= x"0113" & x"00"; -- Time adjustment for bank 1

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"3B" =>

ad_config_reg <= x"0122" & x"00"; --Time adjustment for bank 2

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"3C" =>

ad_config_reg <= x"0123" & x"00"; -- Time adjustment for bank 2

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"3D" =>

ad_config_reg <= x"0132" & x"00"; -- Time adjustment for bank 3

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"3E" =>

ad_config_reg <= x"0133" & x"00"; -- Time adjustment for bank 3

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"3F" =>

ad_config_reg <= x"0142" & x"00"; --Time adjustment for bank 4

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"40" =>

ad_config_reg <= x"0143" & x"00"; --Time adjustment for bank 4

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"41" =>

ad_config_reg <= x"0152" & x"00"; -- Time adjustment for bank 5

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"42" =>

ad_config_reg <= x"0153" & x"00"; -- Time adjustment for bank 5

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"43" =>

ad_config_reg <= x"0160" & x"00"; -- timestamp signal on the LSB of the output samples. Only supported in decimate-by-1(DDC bypass) modes

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

--------------------------------------------------------------------------------------------------------------------204B

when x"44" =>

ad_config_reg <= x"0200" & x"00"; --Always set CAL_EN before setting JESD_EN ;Always clear JESD_EN before clearing CAL_EN--------------------------

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"45" =>

ad_config_reg <= x"0201" & JMODE; -- JMODE

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"46" =>

ad_config_reg <= x"0202" & x"1F"; -- K is the number of frames per multiframe 32

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"47" =>

ad_config_reg <= x"0203" & x"01"; -- Set this bit to 0 to request JESD204B synchronization

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"48" =>

ad_config_reg <= x"0204" & x"06"; --Use the TMSTP+/- differential input for SYNC~ function

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"49" =>

ad_config_reg <= x"0205" & x"00"; -- Test mode RAMP 04

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"4A" =>

ad_config_reg <= x"0206" & x"00"; -- Specifies the DID (Device ID)

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"4B" =>

ad_config_reg <= x"0207" & x"03"; -- Use K28.7 (default) (JESD204B compliant) 00

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

-- when x"4C" =>

-- ad_config_reg <= x"8208" & x"00"; -- JESD_STATUS 6:LINK_UP;2:PLL_LOCKED

-- NEED_DELAY <= x"00000000";

-- BIR <= '1';

when x"4D" =>

ad_config_reg <= x"0209" & x"00"; -- powered down

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"4E" =>

ad_config_reg <= x"020A" & x"00"; -- enable extra lanes

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"4F" =>

ad_config_reg <= x"020B" & x"00"; -- enable extra lanes B

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

------------------------------------------------------------------------------------------------------DDC

when x"50" =>

ad_config_reg <= x"0210" & x"00"; -- DDC_CFG

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"51" =>

ad_config_reg <= x"0211" & x"F2"; -- Over-range threshold 0

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"52" =>

ad_config_reg <= x"0212" & x"AB"; -- Over-range threshold 1.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"53" =>

ad_config_reg <= x"0213" & x"0F"; -- Enables over-range status output pins when set high.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"54" =>

ad_config_reg <= x"0214" & x"00"; -- NCO frequency and phase for DDC

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"55" =>

ad_config_reg <= x"0215" & x"00"; -- select the active NCO

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"56" =>

ad_config_reg <= x"0216" & x"02"; -- Digital channel input select

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"57" =>

ad_config_reg <= x"0217" & x"00"; -- 2-bit NCO frequency word

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"58" =>

ad_config_reg <= x"0218" & x"00"; -- 2-bit NCO frequency word

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"59" =>

ad_config_reg <= x"0219" & x"02"; -- initialize the NCO phase

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"5A" =>

ad_config_reg <= x"0219" & x"02"; -- initialize the NCO phase

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"5B" =>

ad_config_reg <= x"0220" & x"C0"; -- NCO Frequency

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"5C" =>

ad_config_reg <= x"0221" & x"00"; -- NCO Frequency

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"5D" =>

ad_config_reg <= x"0222" & x"00"; --NCO Frequency

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"5E" =>

ad_config_reg <= x"0223" & x"00"; -- NCO Frequency

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"5F" =>

ad_config_reg <= x"0224" & x"00"; -- NCO Phase

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"60" =>

ad_config_reg <= x"0225" & x"00"; -- NCO Phase

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"61" =>

ad_config_reg <= x"02B0" & x"00"; -- SYSREF Calibration ;Program SRC_CFG before setting SRC_EN. Ensure that ADC calibration is not currently running before setting SRC_EN.

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"62" =>

ad_config_reg <= x"02B1" & x"05"; -- SRC_CFG

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"63" =>

ad_config_reg <= x"02B0" & x"00"; --

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

-- when x"64" =>

-- ad_config_reg <= x"82B2" & x"00"; -- SYSREF Calibration Status;;SRC_DONE ;BIT1

-- NEED_DELAY <= x"00000000";

-- BIR <= '0';

-- when x"65" =>

-- ad_config_reg <= x"82B3" & x"00"; -- SYSREF Calibration Status

-- NEED_DELAY <= x"00000000";

-- BIR <= '0';

-- when x"66" =>

-- ad_config_reg <= x"82B4" & x"00"; -- SYSREF Calibration Status

-- NEED_DELAY <= x"00000000";

-- BIR <= '0';

when x"67" =>

ad_config_reg <= x"02B5" & x"00"; -- DEVCLK Aperture Delay

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"68" =>

ad_config_reg <= x"02B6" & x"00"; -- DEVCLK Aperture Delay

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"69" =>

ad_config_reg <= x"02B7" & x"00"; -- DEVCLK Aperture Delay

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"6A" =>

ad_config_reg <= x"02B8" & x"00"; -- he ramp rate

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"6B" =>

ad_config_reg <= x"02C1" & x"3F"; --Alarm Status Register

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"6C" =>

ad_config_reg <= x"02C2" & x"3F"; --Alarm Mask

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"6D" =>

ad_config_reg <= x"0061" & x"01"; -- Calibration Enable. Always set CAL_EN before setting JESD_EN. Always clear JESD_EN before clearing CAL_EN.

NEED_DELAY <= x"0000000000800000";

BIR <= '0';

when x"6E" =>

ad_config_reg <= x"0200" & x"01"; -- Always set CAL_EN before setting JESD_EN ;Always clear JESD_EN before clearing CAL_EN

NEED_DELAY <= x"0000000000800000";

BIR <= '0';

when x"6F" =>

ad_config_reg <= x"006C" & x"00"; -- CAL_SOFT_TRIG

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"70" =>

ad_config_reg <= x"006C" & x"01"; -- CAL_SOFT_TRIG

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

when x"71" =>

ad_config_reg <= x"8208" & x"00"; -- JESD_STATUS 6:LINK_UP;2:PLL_LOCKED

NEED_DELAY <= x"0000000000100000";

BIR <= '1';

when x"72" =>

ad_config_reg <= x"806A" & x"01"; -- foreground calibration has completed

NEED_DELAY <= x"0000080000100000";

BIR <= '1';

when x"73" =>

ad_config_reg <= x"0000" & x"B0"; -- foreground calibration has completed

NEED_DELAY <= x"0000000000100000";

BIR <= '1';

when others =>

ad_config_reg <= x"0003" & x"03"; -- ID

NEED_DELAY <= x"0000000000000000";

BIR <= '0';

end case;