Part Number: ADS1271

Other Parts Discussed in Thread: ADS1250,

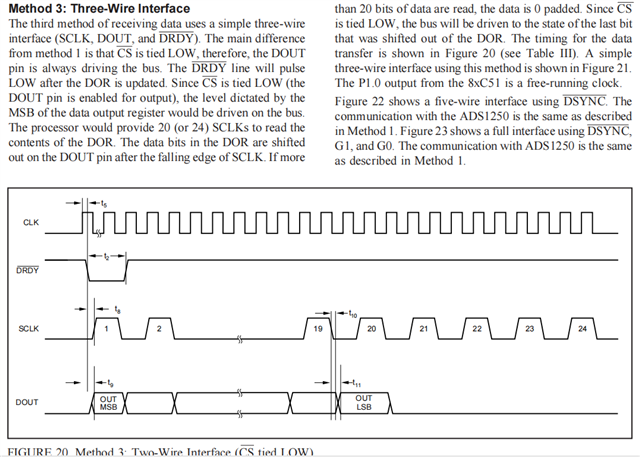

老的ADS1250,供电、加上外部有源晶振后,没有CPU,就可以自发发送DRDY。 P1

P1

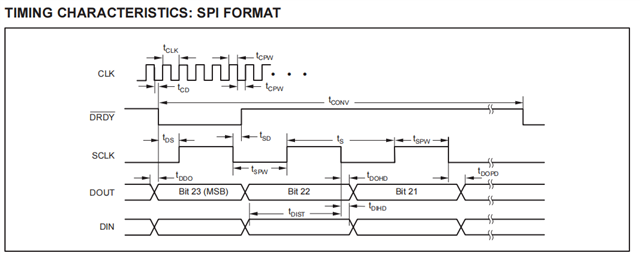

但是我看了说明书,新的ADS1271必须在DRDY那个ready的小窗口内读取到一组sclk,drdy才能正常,正常如右图P2。 P2

P2

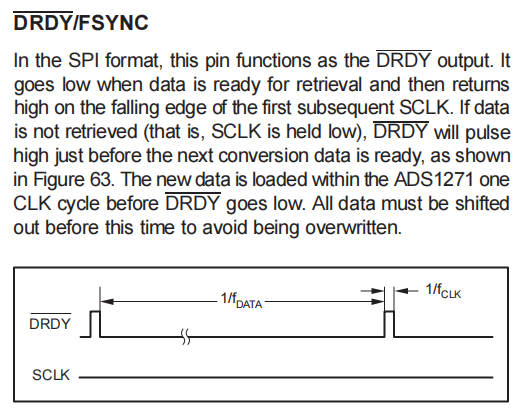

我用gpio模拟spi,发现确实如此,如果不发送sclk,drdy完全错误(即如右图),高低电平完全相反P3。 P3

P3

如果至少发一组sclk,那么/drdy就正确,如图P2。