Part Number: ADS127L21

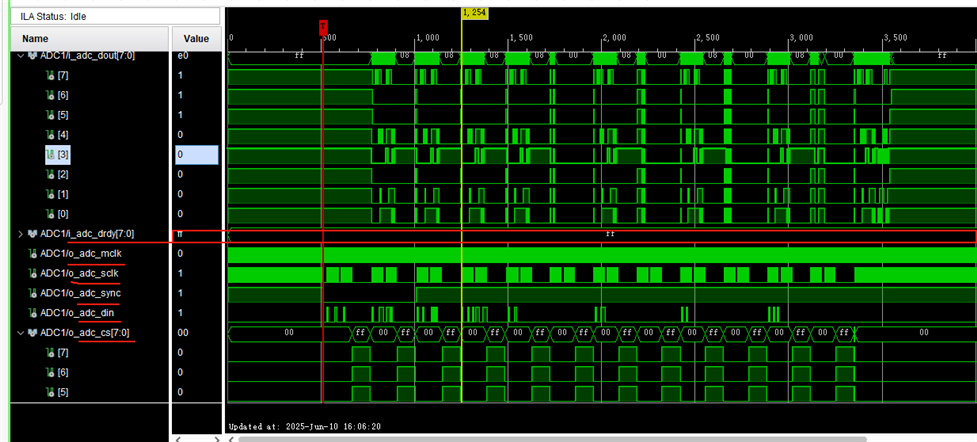

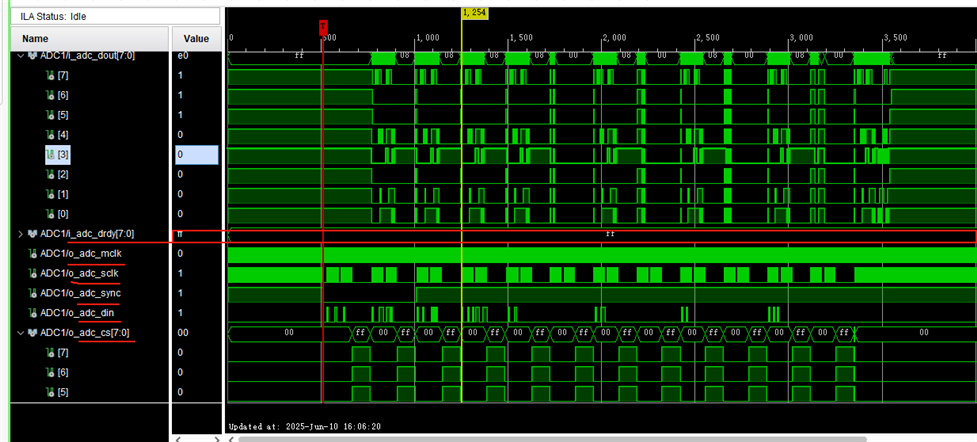

在项目中采用了FPGA连接ADS127L21进行数据采集,驱动程序中设置了MCLK为24.576MHZ,sclk为12.288Mhz,下图为时序图,将start拉高,CS拉低,SDI信号写入了CONFIG1/2/3和FILTER1寄存器,也可以读出数据,但是就没有有效的DRDY信号出现,请帮忙分析一下是什么原因。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: ADS127L21

在项目中采用了FPGA连接ADS127L21进行数据采集,驱动程序中设置了MCLK为24.576MHZ,sclk为12.288Mhz,下图为时序图,将start拉高,CS拉低,SDI信号写入了CONFIG1/2/3和FILTER1寄存器,也可以读出数据,但是就没有有效的DRDY信号出现,请帮忙分析一下是什么原因。