Dear

我想讓 HOST_IRQ 腳位在每次影片撥放結束的時候有所動作,

依照 FPGA User's Guide 中 4.4 Host IRQ Interrupt Signal 所述,以及 4.1.6 Example 5: Display 3+ Videos/Images Seamlessly 的步驟嘗試:

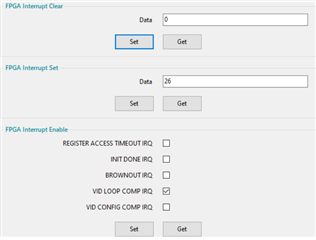

但都沒有效果,只要Interrupt Enable 有任何一個被設置,HOST_IRQ 就都維持是High,無埨我如何設置 FPGA Interrupt Set or Clear......

請問是不是只要將FPGA Interrupt Clear設置為1或0,應該就可以清除FPGA Interrupt Set的狀態,HOST_IRQ也就會再下一次中斷響應時改變狀態呢?還是我理解錯誤呢?

還是此動作無法藉由DLP Control Program 15.1.0.26來模擬達成,一定要使用MCU呢?

請問是否有更詳細有關中斷操作與HOST_IRQ的使用說明呢?

謝謝。